# OAs de Engenharia de Computação para a Educação Básica: Despertando o Interesse Científico e Tecnológico

**Cauan T. Machado<sup>1</sup>, Júlia R. Valverde<sup>1</sup>, Calebe Conceição<sup>1</sup>, Rodolfo B. de B. Garcia<sup>1</sup>**

<sup>1</sup>Departamento de Computação – Universidade Federal de Sergipe (UFS)

{cauan.machado, julia.rocha, calebe, rodolfo.botto}@dcomp.ufs.br

**Abstract.** *This work presents the development of two complementary Learning Objects (LOs) aimed at introducing Computer Engineering concepts in basic education. The first LO integrates a mobile application with an embedded system using an Arduino Nano, allowing the visualization of binary additions on seven-segment displays. The second LO involves the 3D modeling and printing of disassemblable transistors (MOSFET and BJT), facilitating the structural understanding of these components. The methodology is based on incremental prototyping and active learning principles. Expected outcomes include increased student engagement, improved comprehension of hardware concepts, and encouragement of scientific and technological interest.*

**Resumo.** *Este trabalho apresenta o desenvolvimento de dois Objetos de Aprendizagem (OAs) para introdução de conceitos de Engenharia de Computação no ensino básico. O primeiro OA integra uma aplicação móvel e um sistema embarcado com Arduino Nano, permitindo a visualização de somas binárias em displays de sete segmentos. O segundo OA consiste na modelagem e impressão 3D de transistores desmontáveis (MOSFET e BJT), facilitando a compreensão estrutural desses dispositivos. A metodologia baseia-se em prototipação incremental e fundamentos das metodologias ativas de ensino, aplicados a um contexto de exibição em feiras científicas para o ensino básico. Os resultados esperados incluem maior engajamento estudantil, melhor assimilação de conceitos de hardware e estímulo ao interesse científico e tecnológico.*

## 1. Introdução

Em um mundo digital pós pandêmico, temas como Inteligência Artificial e Engenharia de Software estão presentes em praticamente todos os veículos de mídia social. Consequentemente, a área de Computação e Tecnologias da Informação e Comunicação apresentou um crescimento significativo no número de matrículas entre 2021 e 2022, com aumento de 28,1% no total, sendo 11,2% em cursos presenciais e 45,1% na modalidade de Ensino a Distância [Semesp 2024].

Fica evidente, assim, o interesse da juventude em estudar cursos da área de Tecnologias da Informação. No entanto, grande parte desse público ainda apresenta dificuldades significativas em compreender os pilares fundamentais da computação, especialmente os relacionados ao funcionamento de sistemas em nível de hardware e lógica digital. O desempenho costuma ser abaixo do esperado em disciplinas introdutórias, como Sistemas Digitais e Arquitetura de Computadores. Conceitos como bits, bytes, níveis de tensão, transistores e portas lógicas ainda são percebidos como abstratos ou distantes da realidade

prática, o que conflita com um nicho da tecnologia próspero, repleto de oportunidades de trabalho e carente de inovação.

Uma forma de contornar essa falta de interesse é por meio da antecipação da apresentação desses conceitos para o contexto pré universitário, como ocorre com áreas como Inteligência Artificial e Desenvolvimento de Software. Infelizmente, o ensino formal de Tecnologia e Computação na grade curricular do ensino básico, embora obrigatório pela BNCC desde 2017, ainda não está consolidado no país [UNDIME 2023]. Diante desse cenário, torna-se essencial o desenvolvimento de ferramentas educacionais que tornem o conhecimento técnico mais acessível e concreto para estudantes da educação básica.

Nesse contexto, o presente artigo documenta o desenvolvimento de dois Objetos de Aprendizagem (OAs) complementares. O primeiro consiste em uma aplicação móvel que permite realizar e visualizar somas binárias remotamente, promovendo a Aprendizagem Significativa proposta por David Ausubel em tópicos introdutórios à computação [Ausubel 1963]. O segundo OA trata da construção de modelos tridimensionais desmontáveis de transistores dos tipos CMOS e BJT com o objetivo de tornar seu funcionamento mais compreensível e tangível.

Ambos os objetos integram um projeto voltado à popularização do ensino de computação para públicos escolares por meio de exposição em feiras de ciências. A iniciativa visa não apenas ampliar a compreensão dos conteúdos técnicos, mas também fomentar o surgimento de futuros talentos na área, com ações de divulgação científica e tecnológica.

Este artigo está estruturado da seguinte forma: na Seção 2, são apresentados os principais conceitos teóricos que embasaram a construção dos Objetos de Aprendizagem; a Seção 3 descreve a metodologia empregada; em seguida, detalha-se o processo de desenvolvimento dos objetos; e, por fim, discutem-se os resultados esperados em eventos voltados à Computação e à Microeletrônica.

## 2. Referencial Teórico

A seguir, serão apresentados alguns conceitos fundamentais que sustentam o desenvolvimento dos dispositivos propostos e sua utilização no meio escolar para o ensino de Engenharia de Computação, de modo a contextualizar e embasar teoricamente esta pesquisa.

### 2.1. Objetos de Aprendizagem

Objetos de aprendizagem (OAs) constituem recursos digitais ou físicos reutilizáveis, desenvolvidos para oferecer suporte ao ensino [Wiley 2002]. A essência desses objetos reside na capacidade de serem reaproveitados em diferentes contextos educacionais, promovendo não apenas flexibilidade didática, mas também a personalização do aprendizado.

Conforme argumentam [Sinclair and Baccaglini-Frank 2016], o uso de tecnologias digitais interativas na educação primária pode transformar significativamente os processos de ensino e aprendizagem. Essas tecnologias — como softwares educacionais, aplicativos e dispositivos físicos interativos — favorecem novas formas de engajamento, permitindo que os estudantes explorem conceitos de maneira mais dinâmica e personali-

zada. Nesse contexto, o estudante que interage com a OA de forma ativa e significativa tende a apresentar maior eficácia na construção do conhecimento [Ferreira et al. 2017].

Além disso, [Goodfellow 2016] observa que a manipulação física do hardware, associada à interação visual e prática com software podem ajudar a despertar a curiosidade para entender o funcionamento de sistemas computacionais. Esse maior interesse pode influenciar positivamente o processo de aprendizagem, bem como motivar o estudante de ensino básico a querer se aprofundar nesse meio futuramente.

## 2.2. Transistores

O transistor é um componente eletrônico fundamental para a evolução tecnológica dos computadores e foi historicamente responsável pela sua miniaturização e popularização. Sua invenção, em 1947 nos laboratórios Bell, transformou permanentemente a eletrônica ao substituir as válvulas que eram utilizadas nos primeiros computadores eletrônicos. Tal medida permitiu a diminuição do custo energético e o tamanho desses equipamentos, que antes ocupavam salas inteiras, reduzindo também seu custo de produção e, consequentemente, aumentando sua acessibilidade para a população em geral [Iwai and Misra 2022].

Abordamos neste trabalho dois tipos principais de transistores: o transistor de efeito de campo metal-óxido-semicondutor (MOSFET) e o transistor bipolar de junção (BJT). Cada um deles possui suas vantagens e aplicações, porém o MOSFET é mais amplamente utilizado, principalmente em projetos de circuitos integrados, que são fabricados em uma pastilha (chip) simples de silício, por sua capacidade de fabricação em dimensões muito pequenas em comparação com o BJT, e do seu consumo energético reduzido [Sedra and Smith 2007].

Segundo a Lei de Moore, formulada em 1965 [Moore 1998], o número de transistores em um chip dobraria a cada dois anos, mantendo o mesmo custo de fabricação e área de implementação constantes. A lei seguiu válida por tempo suficiente para implicar que um transistor que está presente em um chip atual, como em um processador, possui dimensões nanométricas e, portanto, não pode ser visto a olho nu; tais dimensões extremamente pequenas podem introduzir uma barreira cognitiva para pessoas que estão entrando em contato com esse universo pela primeira vez, já que o fato de não conseguirem visualizar tal dispositivo nas representações no plano bidimensional em que normalmente são apresentados acaba por dificultar a compreensão intuitiva de seu funcionamento, bem como de sua estrutura.

### 2.2.1. Estrutura e Funcionamento do MOSFET

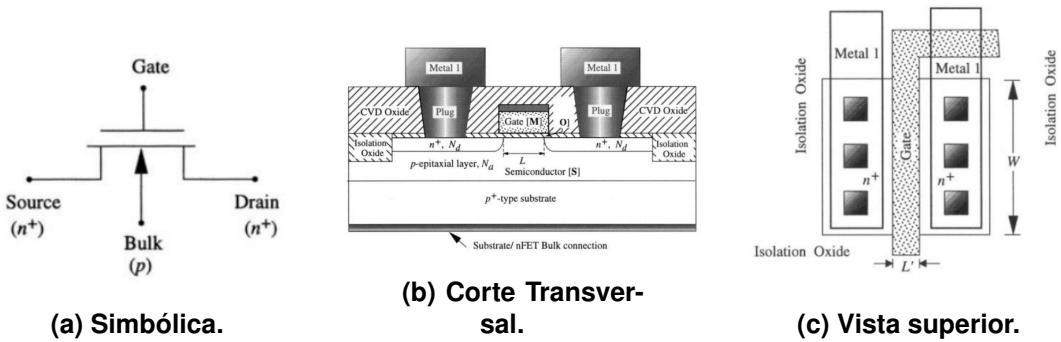

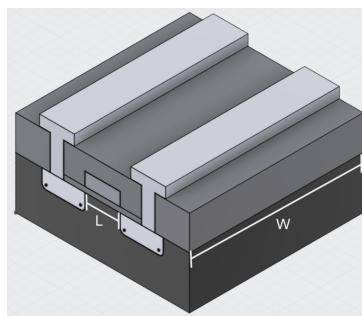

O transistor MOSFET é um dispositivo de 4 terminais nomeados porta (*gate*), fonte (*source*), dreno (*drain*) e *bulk*, apresentado na Figura 1 (a). Em geral, a porta atua como um interruptor que irá permitir ou não a passagem de corrente entre o dreno e a fonte, mediada pela tensão que é aplicada nela.

A região central do dispositivo, conforme ilustrado na Figura 1 (b), consiste no sistema metal-óxido-semicondutor (MOS), composto por uma região condutora, a porta, acima de uma camada de óxido isolante (*isolation oxide*) e, abaixo disso, uma região semicondutora chamada substrato. As regiões nomeadas "n+", correspondem aos terminais

Figura 1. O transistor MOSFET em sua representação.

de fonte e dreno, tendo em cada um deles um pino de metal (plug) condutor acima, e a distância entre esses dois terminais "n+" define o comprimento do canal "L" do MOSFET, um dos parâmetros fundamentais que estabelecem as características elétricas do dispositivo. Além da medida "L", outro parâmetro que se encaixa nesse contexto é a largura do canal "W", melhor observado na Figura 1 (c), que corresponde à região responsável por suportar o fluxo de corrente entre os dois terminais "n+" [Uyemura 1999].

### 2.3. Soma Binária

A consequência imediata da utilização de transistores para representar e operar numericamente é a adoção do sistema binário, uma vez que o transistor é capaz de representar dois estados distintos: 1 para saturado (ligado) e 0 para cortado (desligado). Assim, o sistema decimal, amplamente utilizado em contextos cotidianos, precisa ser convertido para sua forma binária ao nível computacional de máquina. Isso inclui todas as operações numéricas fundamentais, sendo a soma uma das mais essenciais. Compreender como essa operação ocorre é, portanto, um passo fundamental para entender o funcionamento interno de dispositivos digitais.

Nesse sentido, [Pessoa et al. ] descreve detalhadamente como a operação de soma binária é realizada a partir de portas lógicas, desenvolvendo o circuito digital correspondente, bem como explicando seu funcionamento conceitual. A soma binária segue uma lógica semelhante à adição decimal, mas adaptada ao sistema de base dois, que utiliza apenas os dígitos 0 e 1. Por exemplo, no sistema decimal temos  $1 + 1 = 2$ , enquanto no binário essa operação equivale a  $1 + 1 = 10_2$ . Isso significa que o bit da posição atual é 0, e um bit adicional deve ser transportado para a próxima posição à esquerda. Esse bit adicional é chamado de *carry out*, pois é transferido da coluna atual para a seguinte. Ao chegar à próxima posição, esse mesmo bit passa a ser chamado de *carry in*, pois agora é considerado como valor de entrada adicional na nova operação.

- $1 + 1 = 10_2 \rightarrow$  resultado: 0 (na posição atual), *carry out*: 1

- $1 + 1 + \text{carry in} = 11_2 \rightarrow$  resultado: 1, *carry out*: 1

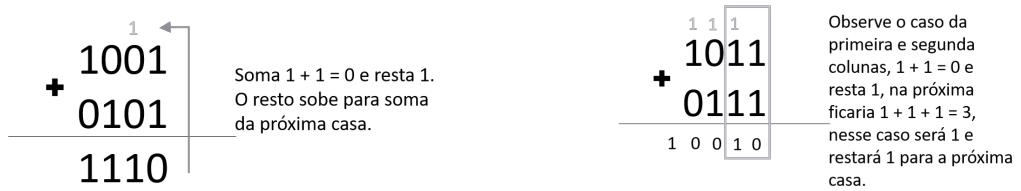

Na soma de números com múltiplos bits, esse mecanismo de propagação do *carry* é fundamental, sendo utilizado repetidamente entre colunas adjacentes. A Figura 2 (a) ilustra uma operação simples, na qual o *carry out* é propagado apenas uma vez. Já a Figura 2 (b) apresenta um exemplo com propagação sucessiva de *carry out*, exigindo o encadeamento de múltiplos estágios para que o resultado correto seja obtido.

**Figura 2. Soma binária**

### 2.3.1. Meia-soma e Soma Completa

No nível lógico, a soma de bits pode ser modelada por dois circuitos combinacionais clássicos: o **meia-somador** (half adder) e o **somador completo** (full adder).

O **meia-somador** realiza a operação entre dois bits de entrada ( $A$  e  $B$ ) e produz duas saídas:

- **Soma:**  $S = A \oplus B$  (XOR)

- **Carry out:**  $C = A \cdot B$  (AND)

Já o **somador completo** considera também o *carry in* oriundo da coluna anterior. Com três entradas ( $A$ ,  $B$ ,  $C_{in}$ ), ele fornece:

- **Soma:**  $S = A \oplus B \oplus C_{in}$

- **Carry out:**  $C_{out} = (A \cdot B) + (C_{in} \cdot (A \oplus B))$

A repetição do somador completo para cada coluna de bits permite a implementação de somadores binários de múltiplos bits, como o utilizado neste projeto. No caso específico do Objeto de Aprendizagem aqui proposto, os valores das parcelas, da soma e os sinais de *carry* são previamente calculados pela aplicação móvel e, então, enviados ao sistema embarcado para exibição nos decodificadores de sete segmentos.

## 3. Descrição dos OAs

Ambos os Objetos de Aprendizagem apresentados neste artigo foram desenvolvidos adotando uma abordagem prática fundamentada nas metodologias ativas de ensino. De fato, a estratégia metodológica usada para atrair os estudantes do ensino básico aos conceitos de Engenharia de Computação, também foi adotada pelos autores como forma de manter o interesse durante todo o desenvolvimento. Desta forma, o estudo da teoria que deveria ser incorporado pelo OA era realizado concomitantemente ao desenvolvimento das práticas, seguindo uma lógica de prototipação incremental, de maneira que sua eficácia pode ser comprovada. Nesta seção são descritos os OAs desenvolvidos e seu funcionamento.

### 3.1. Sistema de Soma Binária

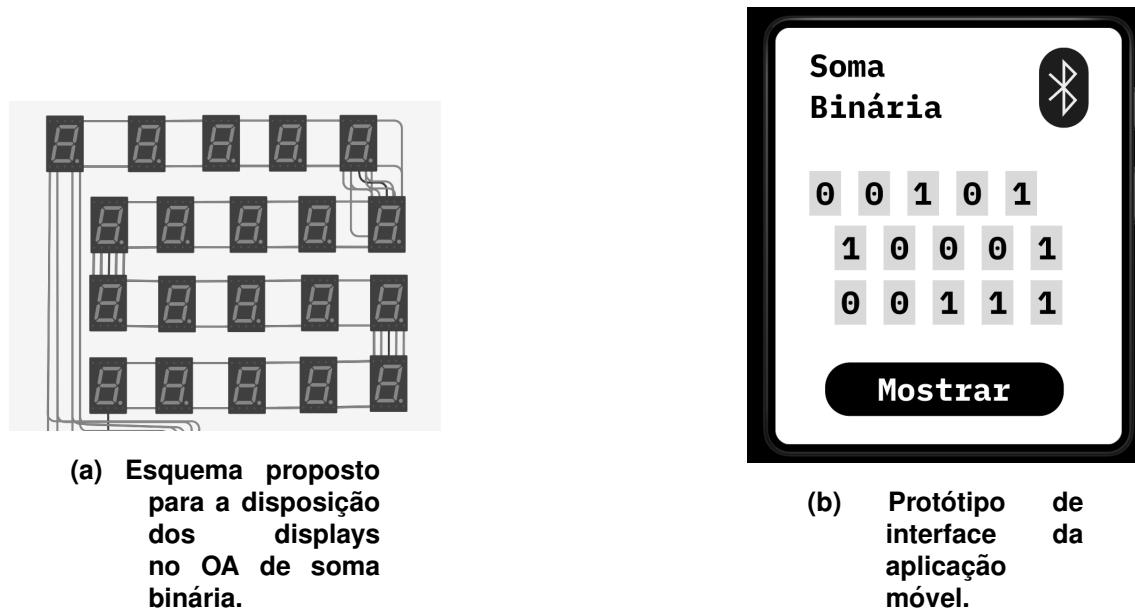

Este OA consiste em um sistema embarcado para a realização e visualização de somas binárias, composto por uma matriz de decodificadores de sete segmentos que será controlada remotamente por meio de uma aplicação móvel. A matriz de displays é organizada

em quatro linhas, sendo a primeira dedicada à visualização dos sinais de *carry out* resultantes da operação, enquanto as três linhas subsequentes representam, respectivamente, a primeira parcela da soma, a segunda parcela e o resultado final da operação. A Figura 3 ilustra tanto o arranjo proposto para os displays (a) quanto o protótipo da interface do aplicativo móvel (b).

**Figura 3. Componentes do sistema de soma binária.**

Visando a reproduzibilidade e a simplicidade na construção do projeto, o microcontrolador selecionado para embarcar o sistema foi o Arduino Nano, por ter custo acessível e por ser amplamente utilizado, inclusive no ensino básico, o que garante vasta documentação gratuita e de qualidade. Para a comunicação foi escolhido o protocolo serial Bluetooth, por meio da integração com o módulo HC05, que também é bastante utilizado e de baixo custo comparado às alternativas. Considerando a necessidade de exibir até 20 dígitos em displays de sete segmentos, número superior ao de portas digitais disponíveis na placa Arduino Nano, a técnica de multiplexação com transistores é empregada, permitindo o controle eficiente de todos os elementos do sistema. O circuito necessita ainda de um conversor de tensão CN6009, que possibilita fornecer a tensão adequada aos decodificadores a partir de uma fonte de 5V.

A aplicação móvel está sendo desenvolvida na plataforma App Inventor 2, mantida pelo Massachusetts Institute of Technology (MIT). Essa ferramenta permite a criação de aplicativos por meio de programação em blocos, o que torna o OA de fácil reprodução, atualização, expansão e manutenção. Neste sistema, a lógica de processamento é centralizada na aplicação móvel. O usuário deve inserir, por meio da interface do aplicativo, as duas parcelas da operação de soma binária. O próprio aplicativo realiza o cálculo da operação e gera como saída não apenas o resultado da soma, mas também os bits correspondentes aos sinais de *carry out*, e deve serializar os dados resultantes, os bits das parcelas, do resultado final e os sinais de *carry*, e transmiti-los via Bluetooth para o microcontrolador Arduino Nano, utilizando o módulo HC05.

O Arduino atua apenas como interface de exibição. Sua função será interpre-

tar os dados recebidos e controlar os decodificadores de sete segmentos por meio da multiplexação com transistores, ativando os segmentos adequados em cada um dos displays. A organização física do sistema permite que os bits sejam representados visualmente, distribuídos entre as quatro linhas da matriz: sinais de *carry out*, primeira parcela, segunda parcela e resultado da operação. Esse modelo de separação entre processamento e exibição visa contribuir para a modularidade do sistema, reduzindo a carga de processamento no Arduino e facilitando futuras atualizações no aplicativo móvel.

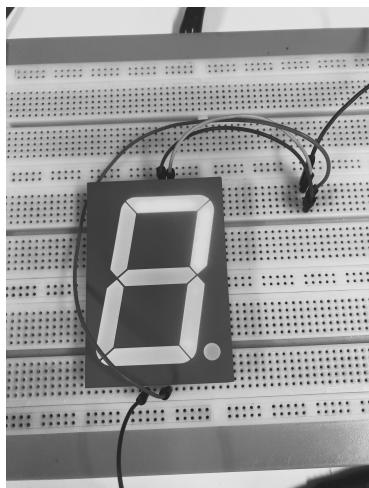

A Figura 4(a) documenta parte da verificação da passagem de corrente em cada segmento dos displays durante os testes iniciais. Enquanto a Figura 4(b) registra uma implementação intermediária do OA em funcionamento, ainda durante a fase de estudos e desenvolvimento, com o **Jogo das Fitas Binárias**, amplamente utilizado por grupos como a IEEE em atividades de divulgação científica<sup>1</sup>. Nesse jogo, o usuário interage com uma sequência de perguntas binárias para descobrir um número oculto, que é exibido nos displays a partir das respostas fornecidas.

**(a)Teste de funcionamento individual dos segmentos.**

**(b)Foto Close-up: Jogo das Fitas Binárias.**

**Figura 4. Registros do funcionamento dos circuitos**

Foi desenvolvido um código em C++ para o Arduino Nano com o objetivo de realizar a multiplexação de cinco displays. Essa técnica é necessária devido ao número limitado de portas digitais do microcontrolador. A multiplexação permite acionar sequencialmente os displays em alta velocidade, de modo que, pela persistência da visão, todos aparentem estar acesos simultaneamente. A implementação foi realizada utilizando a biblioteca TimerOne.h, responsável por gerar interrupções periódicas que controlam a alternância entre os displays enquanto o loop principal processa os dados.

### 3.2. Modelo Tridimensional de Transistores

Considerando que os transistores modernos operam em escalas da ordem de 5 a 10 nanômetros — dimensões menores que as do vírus SARS-CoV-2 — sua compreensão

<sup>1</sup>[https://www.ime.unicamp.br/sites/default/files/1em/material/clubinho\\_de\\_matematica\\_-\\_jogo\\_dos\\_cartoes\\_binarios.pdf](https://www.ime.unicamp.br/sites/default/files/1em/material/clubinho_de_matematica_-_jogo_dos_cartoes_binarios.pdf)

estrutural pode ser abstrata para o público leigo. Assim, a criação de modelos físicos e interativos pretende tornar o ensino mais atrativo e eficaz, especialmente para alunos do ensino fundamental e médio. Este Objeto de Aprendizagem consiste na apresentação de modelos tridimensionais desmontáveis de dois tipos de transistores, o MOSFET e o BJT, para fins comparativos.

Os modelos foram gerados utilizando o software Autodesk Fusion. Este software é um CAD acessível, gratuito para uso não comercial, com interface intuitiva e recursos de aprendizagem abundantes, além de possuir ferramentas suficientes para a realização da modelagem proposta. Os modelos foram projetados através de peças separadas, com representação fiel dos componentes, onde cada elemento estrutural apresentado na seção de fundamentação teórica deve ser gerado com cor distinta para facilitar a identificação visual e o aprendizado. A modelagem prioriza peças com sistema de encaixe que permitam montagem e desmontagem repetidas sem necessidade de cola ou fixadores.

Este objeto de aprendizagem encontra-se em fase de desenvolvimento. Após a fase de modelagem, os protótipos serão materializados por meio de impressão 3D com filamento termoplástico, utilizando uma impressora de modelagem por fusão e deposição (FDM). A etapa de testes avaliará aspectos mecânicos, como o funcionamento e resistência dos encaixes, havendo a possibilidade de retornar à etapa de modelagem para eventuais ajustes, e estabilidade estrutural; e também aspectos pedagógicos, através da apresentação para estudantes do ensino básico. Por fim, será realizada a validação dos modelos MOSFET e BJT, analisando critérios como facilidade de montagem e eficácia de sua utilização para explicar a teoria dos transistores para alunos de ensino fundamental e médio.

Adotou-se no desenvolvimento uma estratégia incremental, priorizando a familiarização com a ferramenta de modelagem e a tradução conceitual dos fundamentos estruturais de transistores MOSFET para um objeto tangível e didático. Desse modo, optou-se por fazer um modelo mais simples e sem encaixes, porém com dimensões parametrizadas, de forma que se pudesse focar no formato das peças e em como elas se disporiaiam para formar o transistor completo.

(a) Esboço transversal do protótipo inicial.

(b) Vista tridimensional do protótipo inicial.

**Figura 5. Primeira versão do modelo 3D do transistor MOSFET.**

A separação de peças foi pensada para que cada componente representasse um elemento funcional que compõe o dispositivo. Logo, a divisão ocorreu da seguinte forma, conforme expresso na Figura 5(a): uma peça para representar todo substrato (9); duas peças iguais (7 e 8) para representar os terminais de fonte e dreno, assim como seus res-

pectivos pinos de condução (2 e 5); uma peça para representar a porta (4); e, por fim, o óxido isolante foi dividido em três peças: uma central (3), que irá envolver a porta, e duas laterais (1 e 6). Dessa forma, todos os elementos essenciais para o funcionamento do transistor estão representados de maneira estruturalmente fiel e como módulos independentes que podem ser analisados individualmente e montados intuitivamente, equilibrando simplificação didática e precisão conceitual.

Aplicando essa ideia, utilizaram-se as ferramentas de esboço e extrusão do Fusion para dar forma às peças e, em seguida, transformar os desenhos bidimensionais em modelos tridimensionais apresentados na Figura 5(b). Essa versão inicial do modelo, contudo, caracterizou-se como um protótipo preliminar, no qual aspectos cruciais para a organização do projeto e para o processo de impressão 3D foram postergados, em benefício da validação da geometria básica de cada peça.

O processo de parametrização foi iniciado desde a etapa de esboço do novo modelo, ao desenhar as peças transversalmente e designar variáveis para cada nova dimensão. À medida que as peças eram desenhadas, algumas medidas passaram a ser definidas em função de variáveis já estabelecidas, de modo que, ao alterar o valor de algum parâmetro, todas as peças cujas dimensões dependem dele também fossem alteradas automaticamente, mantendo a coesão e a proporcionalidade entre os componentes. Todos os parâmetros foram definidos em milímetros com precisão de duas casas decimais, garantindo compatibilidade com o tipo de impressora 3D que será utilizada. Dentre as variáveis estabelecidas, duas se destacam por representar os parâmetros "L" e "W" do transistor, sendo possível editar os componentes em função dessas duas dimensões. Outra variável que se destaca foi nomeada "folga", uma medida extremamente baixa (0,25 mm), que tem a função de estabelecer uma pequena diferença entre as peças que futuramente serão encaixadas, de modo que uma consiga entrar na outra.

Na versão mais recente do modelo (Figura 6), foi necessário fazer mais uma divisão no óxido. A peça central, inicialmente idealizada como uma só, foi dividida em duas: uma mais fina em forma de paralelepípedo (abaixo da porta) e outra que fica por cima, como uma tampa. Essa nova configuração visou facilitar o mecanismo de encaixe.

**Figura 6. Modelo final sem encaixes.**

#### 4. Resultados Esperados e Conclusões

Espera-se que o uso dos Objetos de Aprendizagem desenvolvidos promova um aumento significativo no engajamento dos estudantes com temas de Engenharia de Computação, despertando a curiosidade e motivação por meio da interação prática com o sistema de

soma binária e os modelos de transistor desmontáveis. Além disso, pretende-se verificar melhora na compreensão conceitual de operações em sistema binário e na estrutura interna de transistores, por meio de avaliações de desempenho antes e depois das atividades. No âmbito das habilidades práticas, espera-se que os alunos desenvolvam competências em prototipação eletrônica e modelagem tridimensional, refletidas na qualidade dos protótipos montados e na proficiência na implementação de trechos de código para o Arduino Nano.

Adicionalmente, prevê-se validar a replicabilidade e escalabilidade dos OAs em diferentes contextos escolares, graças à escolha de componentes de baixo custo e de plataformas gratuitas (MIT App Inventor 2 e Autodesk Fusion). Por fim, espera-se que a aplicação destes OAs incentive a continuidade dos projetos pela comunidade escolar, estimulando a criação de oficinas, trabalhos de iniciação científica e feiras de ciências, garantindo a sustentabilidade e evolução contínua das atividades educacionais.

## Referências

- Ausubel, D. P. (1963). *The psychology of meaningful verbal learning*. Grune & Stratton.

- Ferreira, C. L., Botelho, C. S., and Conceição, C. M. (2017). Educare: Investigando a efetividade do uso de objetos de aprendizagem em cursos preparatórios para processos seletivos. In *VII Mostra Científica do IFRS - Campus Restinga*.

- Goodfellow, I. (2016). Deep learning.

- Iwai, H. and Misra, D. (2022). The transistor was invented 75 years ago: A big milestone in human history. *The Electrochemical Society Interface*, 31(4):65.

- Moore, G. E. (1998). Cramming more components onto integrated circuits. *Proceedings of the IEEE*, 86(1):82–85.

- Pessoa, F. A., Oliveira, P. C., Souza, Z. P., and Cavalcante, A. L. Somador binário com decodificador decimal.

- Sedra, A. S. and Smith, K. C. (2007). *Microeletrônica*. Pearson Prentice Hall.

- Semesp, I. (2024). 14º mapa do ensino superior no brasil.

- Sinclair, N. and Baccaglini-Frank, A. (2016). Digital technologies in the early primary school classroom. <https://arxiv.org/abs/1602.03361>. arXiv preprint, arXiv:1602.03361.

- UNDIME (2023). Um em cada cinco municípios do país ainda não tem o ensino de tecnologia no currículo. Brasília, 10 maio 2023.

- Uyemura, J. P. (1999). *CMOS logic circuit design*. Springer Science & Business Media.

- Wiley, D. A. (2002). Learning objects need instructional design theory. In Rossett, A., editor, *The ASTD e-learning handbook*, pages 115–126. McGraw-Hill, New York.