#### ACELERADOR MODULAR PARA ROTEAMENTO

J.S.AUDE, E.B.M.O.PAIVA, E.P.L.AUDE, E.P.L.FILHO, M.F.MARTINS, S.B.PINTO Núcleo de Computação Eletrônica da UFRJ Cidade Universitária - Ilha do Fundão Caixa Postal 2324, 20001 - Rio de Janeiro, RJ

#### RE SUMO

Este artigo descreve uma arquitetura modular dedicada à implementação do algorit mo proposto por Lee para roteamento automático de conexões elétricas em circui tos eletrônicos. O algoritmo de Lee é descrito brevemente e as arquiteturas jã propostas para sua implementação em hardware são discutidas. A arquitetura pro posta no artigo é baseada em duas estruturas pipeline e num esquema especial de organização da memoria que armazena informação sobre a superfície a ser roteada. As modificações do algoritmo de Lee implementadas na arquitetura são discutidas e o funcionamento do hardware é descrito, mostrando-se os algoritmos implementa dos para execução das diferentes fases do algoritmo de Lee. A arquitetura encon tra-se em fase final de detalhamento e resultados de simulação indicam que seu desempenho na execução do algoritmo de Lee será pelo menos 40 vezes melhor do que o de mainframes.

### ABSTRACT

This paper describes a modular hardware router which implements Lee's algorithm. This algorithm is briefly described and the architectures which have already been proposed for its implementation are discussed. The architecture which is proposed in this paper is based on two pipeline structures and on a special organization of the memory which stores information on the layout surface. Both the modifications which have been introduced in Lee's algorithm in the architecture design and the algorithms which are implemented by the hardware for the execution of the different phases of Lee's algorithm are described. At the moment, a detailed design of the architecture is being carried out. Simulation results have shown that the architecture performance will be at least 40 times better than that presented by mainframes in the execution of Lee's algorithm.

Agradecimentos: Os autores agradecem ao CNPq o auxílio dado para a execução do projeto descrito neste artigo.

# 1. INTRODUÇÃO

Devido à crescente complexidade dos circuitos eletrônicos que vem sendo projetados em circuito integrado, a demanda por maior eficiên cia no processamento das ferramentas de CAD tem aumentado substancialmente nos últimos anos. Em consequência, diversas arquiteturas tem sido propostas com o objetivo de ser obter um melhor desempenho na execução de algoritmos de CAD. A maioria destas arquiteturas é baseada na exploração do potencial paralelismo existen te nestes algoritmos. As ferramentas de que tem sido mais frequentemente analisadas pa ra implementação em hardware são os simuladores PFIS86, os verificadores de regras geometri cas [SEIL82], os alocadores [KRAV86] e os rotea dores [RYAN87].

O objetivo do trabalho em desenvolvimento no Núcleo de Computação Eletrônica da UFRJ (NCE/UFRJ) é a construção de uma maquina dedicada capaz de processar eficientemente o algoritmo de roteamento proposto por Lee [LEE61]. A tarefa de um roteador consiste em encontrar e traçar caminhos que interliguem os terminais de componentes que pertençam a um mesmo sinal elétrico. Estes caminhos podem ser traçados em uma

mais camadas de materiais disponíveis para roteamento dos sinais. O algoritmo de Lee é um dos algoritmos mais utilizados na implementação de roteadores. Este algoritmo garante encontrar um caminho entre dois pontos se tal caminho existe e garante que o caminho encontrado é de tamanho mínimo.

No algoritmo de Lee, a superfície a ser roteada é representada por uma matriz de células quadra das. Em princípio, apenas segmentos horizontais ou verticais são geradas pelo algoritmo no tra çado dos caminhos. Para cada conexão a ser fei ta, a execução do algoritmo de Lee passa tres etapas. A primeira delas, a "fase de expan são", é responsável por descobrir se há um cami nho interligando os dois pontos. O procedimento utilizado nesta fase consiste na definição, cada iteração, de uma nova fronteira de celulas a partir da expansão das células da fronteira atual nas direções norte, sul, leste e oeste. Cada célula da nova fronteira é marcada com uma "seta" que aponta na direção da célula cuja pansão originou sua marcação. Inicialmente, fronteira de células é composta de uma única cé lula, a célula que corresponde ao ponto de ori gem do caminho a ser traçado. Na iteração da fase de expansão, uma nova fronteira com no

máximo 4n células é formada. A fase de expansão termina quando a célula que representa o ponto destino é atingida e, portanto, um caminho foi encontrado, ou quando não há mais células na fronteira para serem expandidas, significando que não existe caminho entre os dois pontos. Para um caminho de comprimento " $\ell$ ", expresso em número de células atravessadas, o tempo gasto na fase de expansão é proporcional a  $\ell$ \*\*2.

A segunda fase do algoritmo de Lee é a "fase de retraço". Seu objetivo é traçar o caminho entre os dois pontos encontrado na fase de expansão. O procedimento adotado consiste em, simplesmente, seguir as setas marcadas, partindo da celu la que representa o ponto destino até atingir a célula que representa o ponto de origem do caminho. O tempo gasto na execução desta fase é porporcional ao comprimento "l" do caminho.

A terceira fase do algoritmo é a "fase de reini cialização". Seu papel é preparar a matriz de células que representa a superfície de roteamen to para a execução da fase de expansão da proxima conexão. Basicamente, nesta fase, as células utilizadas no caminho definido pelo retraço são transformadas em células de bloqueio para as proximas conexões e as setas marcadas nas células não utilizadas são apagadas. O tempo gasto nesta fase é proporcional a p\*q, onde "p" e "q" são as dimensões da matriz de células que representa a superfície a ser roteada.

A Seção 2 deste artigo discute algumas das ar quiteturas já propostas para implementação do algoritmo de Lee. Na Seção 3, as modificações no algoritmo básico de Lee implementadas na ar quitetura proposta neste trabalho são discutidas. Ainda nesta seção é feita uma descrição da arquitetura do acelerador. A Seção 4 discute o funcionamento do acelerador em maiores deta lhes. Finalmente, a Seção 5 descreve o estágio atual do projeto, apresentando uma estimativa de desempenho da arquitetura em função de resultados obtidos com um simulador do acelerador.

### ARQUITETURAS PROPOSTAS PARA IMPLEMENTAÇÃO DO ALGORITMO DE LEE

Como as fases de expansão e de reinicialização do algoritmo de Lee são as que mais consomem tempo de máquina, a maioria das arquiteturas propostas para implementação em hardware do al goritmo de Lee visam tornar mais eficiente o processamento destas duas fases.

A maquina "L" de Breuer e Shamsa [BREU81] foi a primeira arquitetura proposta para implementa ção em hardware do algoritmo de Lee. A maquina "L" é uma arquitetura matricial, onde cada processador é associado a uma única célula da matriz que descreve a superfície a ser roteada. Com esta estrutura, na fase de expansão do algoritmo de Lee, a expansão das células de cada fronteira pode ser realizada em paralelo. Este fato faz com que o tempo gasto na expansão se torne proporcional a "l" e não mais a "l\*2" para um caminho de tamanho "l". O uso de uma ar quitetura matricial permite obviamente que a fa se de reinicialização seja feita em paralelo pa

ra todas as células em um único passo. Infeliz mente, a proposta da máquina "L" tem sua aplica ção limitada na prática a problemas de roteamen to em que a superfície pode ser descrita por uma matriz de células de pequenas dimensões.

Visando contornar o problema apresentado maquina "L", Blank, Stefik e Van [BLAN81], propuseram a maquina SAM("Synchronous Active Memory"). A arquitetura desta máquina é também matricial, porém a tecnica de "folding" é utilizada para permitir que a cada dor sejam associadas varias celulas da que descreve a superfície a ser roteada. Com is so, reduz-se a quantidade de circuito necessa ria para implementação da maquina, porem de-se flexibilidade na exploração de paralelis mo nas fases de expansao e de reinicialização do algoritmo. Um esquema semelhante foi também utilizado na maquina WRM [HONG81] em que elementos de uma matriz 8x8 de microprocessado res sao associadas, por um mecanismo "folding", todas as celulas que compoem a ma triz que representa a superfície a ser roteada.

Na maquina IAP proposta por Iosupovici [IOSU86], uma estrutura SIMD também é utilizada. Nesta es trutura, a cada processador está associada uma única célula da matriz. A implementação da quina prevê a utilização de uma matriz chips. Cada chip contem matrizes nxn de proces sadores, onde n=2\*\*k-1. A comunicação chips vizinhos se da através de "k" fios bidire cionais, que permitem o acesso sequencial processadores situados nas bordas vizinhas chips. Iosupovici mostra que esta comunicação sequencial entre os chips, necessária para redu zir o número de fios entre eles, não compromete significativamente o desempenho da maquina, ou seja, o tempo gasto na fase de expansão conti nua sendo proporcional a "l" para um caminho de comprimento "l".

Na maquina ISMA [RYAN87], foi utilizada ideia bastante original para se implementar algoritmo de Lee com uma arquitetura matricial envolvendo um número não muito grande de proces sadores. A proposta nesta arquitetura é tar o algoritmo de Lee em dois passos. meiro passo, considera-se a matriz que represen ta a superfície a ser roteada dividida em sub matrizes. Cada submatriz é considerada como uma única celula que pode estar bloqueada ou não de pendendo do grau de ocupação das suas celulas. A cada submatriz é associado um processador da maquina ISMA. Como resultado deste primeiro pas so, um roteamento aproximado é definido, deter minando-se as submatrizes que devem ser atraves sadas pelo caminho a ser traçado. No segundo passo, o roteamento detalhado em cada uma submatrizes utilizadas no primeiro passo é rea lizado em sequência. A matriz de processadores deve ter dimensões iguais às das submatrizes. A implementação do algoritmo de Lee na ISMA na forma descrita não garante encontrar o menor caminho entre dois pontos.

Uma arquitetura diferente para implementação do algoritmo de Lee em hardware foi apresentada por Rutenbar et al. [RUTE84]. Nesta arquitetu

ra, matrizes 3x3 de processadores dispostas em uma estrutura de pipeline são responsáveis pela realização em paralelo da expansão de diferen tes fronteiras. O número de matrizes no pipeli ne determina o número de fronteiras que ser expandidas em paralelo. O pipeline é alimen tado através de uma operação de varredura quencial das células da matriz que representa a superficie disponivel para layout. Para a fase de reinicialização um único estágio do pipeline é utilizado. Esta arquitetura reduz considera velmente o número de circuitos utilizados para implementação da maquina, porem tem uma capaci dade bem mais limitada de exploração do parale lismo existente no algoritmo de Lee.

Won, Sahni e El-Ziq [WON87] propuseram a imple mentação em hardware do algoritmo de Lee usando uma sequência de 3 processadores em pipeline pa ra execução da fase de expansão. Nesta arquite tura a marcação das celulas vizinhas de uma da da célula é feita simultaneamente e, em parale lo, com a leitura de uma nova celula da frontei ra atual a ser expandida e com a adição de no vas celulas à proxima fronteira a ser expandi da. Na maquina proposta por Won et al., apenas uma camada de roteamento é considerada e estágio do pipeline tem seu processamento defi nido por rotinas em software. A arquitetura pro posta neste trabalho e uma extensão da arquite tura proposta por Won et al.

### 3. ARQUITETURA DO ACELERADOR

O objetivo do projeto do NCE/UFRJ é implementar uma arquitetura para execução do algoritmo de Lee que seja realizável na prática com circuitos integrados SSI, MSI e LSI disponíveis no mercado e que possa funcionar como um dispositivo acelerador conectável aos microcomputadores e supermicrocomputadores nacionais. Com isso pretende-se viabilizar o desenvolvimento no país de estações de trabalho para roteamento poderosas e de baixo custo.

As arquiteturas SIMD, embora permitam a explora ção ao máximo do paralelismo existente no algoritmo de Lee, demandam um grande número de circuitos e, consequentemente, requerem o uso de técnicas de integração em larga escala para sua implementação. Um outro ponto a observar é que, para implementação do algoritmo de Lee, o grau de utilização dos processadores existentes em uma arquitetura SIMD é, em geral, muito baixo. Devido a estes fatores este tipo de arquitetura mostrou-se inadequado aos objetivos do projeto.

A arquitetura a ser proposta é uma extensão da máquina desenvolvida por Won, Sahni e E1-Ziq [WON87], com características modulares. O módu lo básico do acelerador tem capacidade para operar com áreas de roteamento de até duas camadas e dobra o paralelismo explorado pela máquina de Won sem subutilizar o hardware adicional neces sário. Esta melhoria de desempenho é alcançada com a incorporação na arquitetura da estrutura de "pipeline" utilizada no processador RPS [RUTEN84]. Um melhor desempenho também é obtido porque os estágios das estruturas de pipeline são implementados diretamente em hardware e não

em software como na maquina de Won et al. Atra vés da adição de outros módulos básicos, o ace lerador se torna capaz de atacar problemas em superfícies com múltiplas camadas de roteamento e representadas por matrizes de grandes dimen sões. Além disso, o acelerador passa a poder rotear em paralelo conexões confinadas a certas regiões da superfície global de roteamento.

Três alterações do algoritmo básico de Lee fo ram implementadas nesta arquitetura. A Seção 3.1 descreve estas alterações e a Seção 3.2 des creve a arquitetura propriamente dita.

# 3.1. Alterações no Algoritmo Básico de Lee.

A primeira alteração introduzida no algoritmo básico de Lee diz respeito à conexão de sinais com mais de dois pontos. Para implementação des ta facilidade, a fase de reinicialização marcar como celulas destino, ao inves de las de bloqueio, as celulas utilizadas centes a um mesmo sinal. Desta forma, para cada conexão adicional de um mesmo sinal, uma célula origem é definida e todas as células já utilizadas nas conexões anteriores deste mesmo sinal são consideradas celulas destino. Com es te mecanismo, ligações em "T" podem ser produzī das pelo roteador. Quando isto é indesejavel, ligações em "cadeia" são realizadas e, neste ca so, a fase de reinicialização define que todas as celulas, com exceção da celula de origem pertencentes à conexao anterior de um sinal são células de bloqueio para as próximas conexões. A célula de origem é definida como célula desti no para a proxima conexao do sinal. Uma exceção ocorre na primeira ligação, já que a célula des tino desta ligação deve permanecer como celula destino para a ligação seguinte.

A segunda alteração implementada visa habilitar o algoritmo a trabalhar com mais de uma camada para roteamento. Basicamente, a alteração intro duzida no algoritmo consiste em realizar a fase de expansão considerando que a matriz de las é uma matriz tridimensional. Ao se realizar a expansão para uma celula em um dado plano, as celulas vizinhas situadas em planos inferiores ou superiores são também marcadas. Para viabili zar a implementação desta modificação, duas no vas setas, além das quatro ja existentes, sao utilizadas: seta apontando para cima e apontando para baixo. Comumente, em problemas de roteamento em multiplas camadas, a cada cama da e associada uma direção preferencial de teamento, horizontal ou vertical, que determina a ordem de precedência na marcação de setas em cada camada. Expansões que impliquem em mudança de camada só prevalecem quando não é possivel expandir na direção preferencial da camada cor rente e existe possibilidade de expansão na di reção preferencial da camada para onde se esta

A terceira e última alteração introduzida no algoritmo básico de Lee visa melhorar o desempenho do algoritmo, evitando que cada conexão roteada crie bloqueios que certamente dificultarão o roteamento de conexões subsequentes. O mecanismo utilizado para isso foi a introdução de

custo diferenciado para as celulas que compoem a matriz que representa a superfície a ser teada. Basicamente, a ideia consiste em atri buir custo mais elevado para células dos pinos a serem interconectados, custo medio para células sem nenhuma célula vizinha ocupada e custo mais baixo para células vizinhas de cé lulas ja utilizadas por conexoes anteriores. Com este esquema, busca-se evitar o bloqueio em posições adjacentes aos pinos dos componentes e dos conectores e busca-se, sempre que possível, "empilhar" conexões traçadas próximas umas outras. Para implementação deste mecanismo custo, tanto a fase de expansão quanto a de reinicialização tiveram de ser modificadas. Na fase de expansao, celulas na fronteira a ser expandida que possuam custo diferente de 1 não sofrem expansão. O custo delas é subtraído de 1 e, com este novo custo, elas passam a fazer par te da fronteira a ser expandida na proxima ite ração do algoritmo. Com isso, o algoritmo Lee deixa de gerar o caminho de comprimento mi nimo e passa a gerar o caminho de custo minimo. É interessante notar que o esquema de custo pro posto tem um caráter dinâmico: o custo das celu las é redefinido à medida que o roteamento pros segue. Portanto, ao se completar uma ligação, o algoritmo deve recalcular o custo de cada celu la em função dos critérios acima estabelecidos. Apenas tres valores de custo estão sendo utili zados: 1, 2 e 3. A utilização ou não de diferenciado para as celulas é uma opção usuário.

# 3.2. Descrição da Arquitetura.

O aspecto fundamental do projeto do acelerador de roteamento é o uso de um esquema especial de banqueamento para a organização da "memória de placa", a memoria que armazena as celulas compoem a matriz de representação da superfície a ser roteada. Na estrutura de banqueamento uti lizada ha 8 bancos distintos. Dois grupos podem ser definidos: o grupo I, contendo os bancos 0, 1, 2 e 3 e o grupo II, contendo os bancos 4, 5, 6 e 7. As células pertencentes aos bancos grupo I tem todas as suas celulas vizinhas bancos do grupo II e vice-versa. Duas vantagens importantes resultam desta estrutura de banquea mento. Em primeiro lugar, a expansão de cada ce lula pode ser feita em paralelo, já que as célu las vizinhas a serem marcadas estao em bancos diferentes que podem ser acessados concorrente mente. Em segundo lugar, durante a fase de pansão do algoritmo, pode-se sempre expandir em paralelo células pertencentes a duas fronteiras subsequentes, ja que uma delas causara expansão para células do grupo I e a outra fará expansão para células do grupo II.

Visando explorar as vantagens apontadas acima, duas sequências de processadores em "pipeline" são usadas na implementação do acelerador para a fase de expansão do algoritmo. Cada sequência processa a expansão das células pertencentes a uma de duas fronteiras subsequentes. Estas se quências de processadores em "pipeline" são com postas de 3 estágios. O primeiro estágio lê a próxima célula a ser expandida da memória que

armazena a fronteira em expansão. O segundo es tágio realiza a expansão propriamente dita, acessando em paralelo os bancos necessários da memória de placa. Finalmente, o terceiro está gio acrescenta à memória que armazena a fronteira a ser expandida pela outra sequência de processadores as células marcadas pelo segundo es tágio.

A fim de permitir que a operação realizada pelo terceiro estágio possa ser feita de forma corrente para as células marcadas na fase de ex pansão, a informação é armazenada na de fronteira" de forma codificada. Esta codifi cação indica as coordenadas da celula que origem à expansão e identifica as celulas nhas que devem fazer parte da próxima frontei ra. Na verdade, esta memoria esta organizada basicamente, em 2 conjuntos de 2 bancos. dos bancos, são armazenadas as celulas da teira pertencentes aos bancos 0, 1, 2 e 3 da me mória de placa e no outro banco as células per tencentes aos bancos 4, 5, 6 e 7. A cada instan te de tempo, uma sequência de processadores le de um banco de um conjunto e a outra sequência de processadores escreve no mesmo banco do tro conjunto. Procedimento analogo ocorre relação ao outro banco.

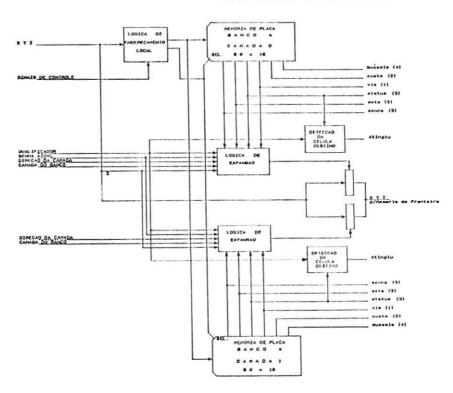

O módulo básico do acelerador compreende estas duas sequências de processadores em "pipeline" e é capaz de operar em até duas camadas de ro teamento. Para que isto seja possível o número de bancos de memória de placa deve ser duplica do. Para atualização da memória de fronteira, optou-se por economia de memória e realização das operações de atualização no estágio 3 do pipeline em dois passos: em cada passo as célu las de uma única camada são adicionadas ao com teúdo da memória de fronteira. A organização in terna do módulo básico do acelerador é mostrada esquematicamente na Figura 1.

Figura 1: Arquitetura do Módulo Básico

Na memória de placa, 16 bits são utilizados pa ra o armazenamento de cada celula. Tres bits de finem o status da célula, isto é, se a célula é um bloqueio, se a celula representa um destino, se a célula representa um ponto de um barramento de alimentação, etc. Quatro outros bits, denominados bits de "bussola", são utili zados para caracterizar o tipo de desenho deve ser associado aquela celula quando da im pressão dos resultados. Dois bits definem o cus to da celula. Tres outros bits definem, na fase de expansão, a "senha" que deve ser associada aquela célula. A senha é necessária para indi car se, numa da iteração da fase de expansão, uma célula pode ser marcada ou não. A célula só pode ser marcada se sua senha indicar que ainda não foi marcada (senha=0) ou que sua mar cação ocorreu nesta mesma iteração. Dos quatro bits restantes, três são utilizados para repre sentar a seta e o outro, o bit de "via", indicar se é permitido haver furo de passagem para outra camada naquela celula.

O módulo básico do acelerador é projetado para armazenar uma matriz de células do dimensões 256 x 256 x 2. Consequentemente, como a memória de placa está dividida em 8 bancos por camada, cada banco é implementado como uma memória de 8K palavras de 16 bits.

Cada palavra da memoria de fronteira deve arma zenar as coordenadas x, y e z da celula expandi da, os valores de custo dos seus quatro vizi nhos e a senha a ser usada na expansão destes vizinhos. Valores de custo iguais a zero indi cam que uma dada celula vizinha nao pertence a nova fronteira. Consequentemente, 28 bits necessários por palavra. O tamanho máximo de uma fronteira em cada camada de um modulo co é inferior a 1K. Portanto, a memoria de fron teira de cada módulo básico é implementada por 2 grupos de 2 memorias 2K x 28.

Não é apenas na fase de expansão que o acelera dor pode produzir ganho de velocidade através da exploração de paralelismo. Na fase de reinicialização, os oito bancos da memoria de placa são varridos concorrentemente. Neste processo de varredura o valor de senha armazenado em ca da célula é zerado. Com este esquema, 16K ci clos (8K ciclos de leitura e 8K ciclos de escrita) de acesso à memoria são realizados na fase reinicialização. Este número se mantém constante mesmo que diversos módulos básicos estejam sendo utilizados, já que os módulos básicos operam em paralelo.

A fase de retraço introduz um aumento de tempo muito pequeno no algoritmo de Lee e dá pouca margem à exploração de paralelismo. Consequente mente, na arquitetura em desenvolvimento, esta fase é implementada sob controle de um micro processador. Com isso, maior flexibilidade é obtida na programação desta fase que é responsa vel não só por redefinir os campos de status e bússola das células utilizadas no caminho traça do bem como por atualizar os campos de custo e via das células vizinhas ao caminho. Tal flexi bilidade de programação é desejável principal mente porque ela permite que diferentes políti

cas de atribuição de custo às células sejam utilizadas sem modificação do hardware.

Como já foi dito, os diferentes módulos do ace lerador trabalham de forma concorrente na fase de reinicialização. Na fase de expansão, o tra balho concorrente dos módulos é também vel. A condição para que isso ocorra é que ca da modulo esteja lidando com ligações contidas na região de 256x256 celulas por ele coberta. Quando um dos modulos detecta que a que ele deve realizar envolve o uso de regiões diferentes da sua, este módulo solicita o con trole global da maquina. Uma vez assumido controle global, os processadores do modulo passam a ter acesso às memórias de placa resi dentes nos demais modulos. A expansão é reali zada com o trabalho cooperativo de todos os mo dulos, porem, em princípio, apenas um modulo está ativo a cada instante de tempo. O módulo ativo no momento é aquele que detém o controle global da maquina e que executa a fase de pansão. Quando o módulo ativo encerra a expan são de uma fronteira, ele passa o comando glo bal da maquina para um outro modulo que possua celulas a serem expandidas dentro da fronteira.

### 4. FUNCIONAMENTO DO ACELERADOR

Para um melhor entendimento do funcionamento do acelerador, é importante detalhar os algo ritmos implementados, em hardware, para as fa ses de expansão e reinicialização e, em soft ware, para a fase de retraço.

Conforme ja foi mencionado, a fase de expansão é processada em paralelo por duas estruturas de pipeline com três estagios: leitura da memoria de fronteira, expansão propriamente dita e escrita na memoria de fronteira. O algoritmo executado pelo primeiro estagio é basicamente o seguinte:

Procedimento LeMemoriadeFronteira;

Se endereço de leitura >= limite do conjunto de leitura atual

Então Define conjunto de leitura atual como conjunto de escrita e o conjunto de escrita atual como conjunto de leitura;

Senão Lê informação do conjunto atual d leitura;

Se ha vizinho com custo = 1

Então Gera endereço [x,y,z] deste vizi nho para uso do segundo estágio;

Zera custo deste vizinho;

Se ha outro vizinho com custo = 1

Então Armazena informação atualizada de volta;

Senão Se há vizinho com custo <> 0 Então Autalizacusto;

Senão Incrementa endereço de leitura;

Senão Atualizacusto;

Fim;

Procedimento Atualizacusto;

Decrementa 1 de todos os valores de custo diferentes de zero;

Incrementa o valor da senha;

Se valor da senha > 7 Então senha := 1; Armazena informação atualizada no grupo

Incrementa endereço de leitura;

Fim;

Dois aspectos importantes no procedimento crito devem ser destacados. O primeiro deles que, no máximo, dois acessos à memória de fron teira são feitos na execução do procedimento. Destes acessos, um deles é de leitura e o outro é de escrita. Apenas um acesso de leitura realizado quando a informação lida contém ape nas um vizinho com custo unitario e o custo dos demais vizinhos é zero. O segundo aspecto deve ser destacado é que a execução do procedi mento Atualizacusto pode implicar em conflito no acesso ao conjunto de escrita da memoria de fronteira. Este conflito surge porque o estagio 3 da estrutura de pipeline pode estar neamente requerendo uma operação de escrita nes te conjunto para incluir celulas na nova teira a ser expandida.

O algoritmo executado pelo segundo estágio estrutura de pipeline, responsável pela sao da celula lida, da memoria de fronteira pelo primeiro estágio, é o seguinte:

```

Procedimento de Expansao;

```

Se foi lida Célula pelo primeiro estágio Então Calcula endereço de todos os vizinhos; Para cada vizinho faça, em paralelo:

Se vizinho dentro dos limites do módu

Então Le vizinho na memoria de placa Se status vizinho <> bloqueio e (senha [vizinho] = senha atual ou 0) e seta vizinho tem priorida de menor que

nova seta e

não há mudança de camada ou pode haver via)

Entao seta vizinho := nova seta; senha vizinho := nova senha; Atualiza vizinho na memoria placa:

Guarda custo vizinho para

do terceiro estágio;

Se status vizinho = destino ou (status [vizinho] = barramento de alimentação "X" qualificador do tipo de

na1 = "X") Então atingiu celula destino; Senão Guarda custo vizinho = 0 pa ra uso do terceiro estagio;

É importante notar que também neste procedimen to são realizados no máximo dois acessos a cada banco da memória de placa: um acesso de leitura e outro de escrita.

O terceiro estágio do pipeline armazena na memo ria de fronteira as coordenadas da celula expan dida e o custo de todos os vizinhos marcados pe lo segundo estagio. Para cada modulo, este esta gio deve realizar, em dois passos sequenciais, o armazenamento das informações referentes a ca da uma das duas camadas. Portanto, o procedimen

to executado pelo terceiro estágio envolve no máximo dois acessos de escrita na memória de fronteira. O procedimento executado para cada passo é o seguinte:

Procedimento EscreveMemoriadeFronteira;

Se há vizinho com custo <> 0

Então Escreve informação {[x,y,z], custos e senha atual+1);

Incrementa registro de endereço limite;

Fim;

O algoritmo de retraço que é implementado software e e executado quando a celula destino é atingida pode ser descrito basicamente pelo seguinte procedimento:

```

Procedimento Retraço;

```

Le celula destino;

Enquanto status celula (> início faça Usando seta celula , calcula x,y,z proxima celula;

Atualizastatus;

Atualiza a bussola da celula, consideran do a bussola atual e a seta anterior, se existir;

Se custo dinâmico

Então Redefine custo dos vizinhos;

Se ha mudança de camada na celula

Então Redefine via das celulas vizinhas de forma a impedir mudança de camada nestas celulas;

seta anterior := seta celula ; Lê proxima celula;

Fim;

Procedimento Atualizastatus;

Se ultima ligação de um sinal

Então status celula := bloqueio porque per tence a caminho;

Senao Se topologia da ligação = cadeia

Então Se (não é primeira ligação do sinal e status celula = início)

Entao status [celula] := destino; Senao Se (status celula <> destino ou não é primeira ligação) Então status[celula] := blo queio porque pertence a ca

minho; Senão status [celula] := destino;

O procedimento executado em hardware para a fa se de reinicialização é o seguinte:

Procedimento Reinicialização;

Para todo banco da memoria de placa, faça, em paralelo:

endereço := 0;

Enquanto endereço <= ultimo endereço banco faça:

Lê célula;

senha [celula] := 0; Se ultima ligação

Então Se status celula = destino Entao status celula := bloqueio porque pertence a caminho;

Armazena informação da celula atualiza da:

Fim;

A análise deste procedimento mostra que cada ciclo da fase de reinicialização executa dois acessos à memória de placa: um acesso de leitura e outro de escrita.

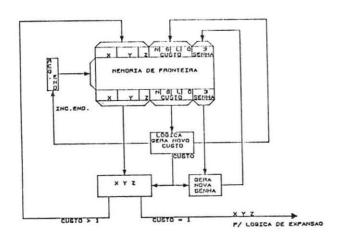

As Figuras 2 e 3 mostram os circuitos de con trole de memoria de placa e da memoria de fron teira, respectivamente, necessários para implementação em hardware dos procedimentos descritos.

# 5. ESTÁGIO ATUAL E PERSPECTIVAS FUTURAS

O projeto de hardware do acelerador se encontra, no momento em fase final de detalhamento da arquitetura. Sua implementação se dará basicamente com uso de memórias MOS estáticas, microprocessadores e alguns circuitos TTL SSI e MSI. Estima-se que cerca de 300 circuitos integrados serão utilizados na implementação do modulo básico do acelerador.

Figura 2. Lógica de Controle da Memória de Placa.

Figura 3. Controle da Memória de Fronteira.

Um simulador da arquitetura do acelerador foi desenvolvido como ferramenta para avaliação do projeto principalmente no que diz respeito a: determinação da melhor partição do acelerador em módulos básicos, avaliação do desempenho do acelerador e medida do grau de utilização dos estágios que compõem os pipelines.

O simulador fornece medidas do tempo gasto em cada fase do algoritmo em relação ao tempo to tal de processamento e da taxa de ocupação dos estágios dos pipelines. Além disso, o simula dor fornece medidas da frequência com que con tenções ocorrem durante o processamento. Basicamente, existem dus situações em que podem ocorrer contenções. A primeira delas é quando um modulo assume o controle global da máquina para completar uma operação de roteamento, for çando que os demais modulos tenham suas atividades suspensas. A segunda situação ocorre em problemas de roteamento em que o custo das ce lulas não é unitário, quando é possível que ha ja conflito no acesso à memória de fronteira.

Resultados ja obtidos com o simulador, sem le var em conta o paralelismo na operação entre módulos, demonstram que, usando-se custo unitario, o roteamento de cerca de 1000 ligações de

comprimento médio igual a 200 pode ser realiza do após cerca de 200 milhões de ciclos de quinas. A cada ciclo corresponde a execução das tarefas de um estágio do pipeline na fase de expansão ou a uma operação concorrente zeramento da senha de 8 celulas na fase de rei nicialização. Considerando-se que as fases de expansão e de reinicialização são as que mais consomem tempo de maquina na execução do algo ritmo de roteamento e que cada ciclo duas fases realiza basicamente dois acessos a memoria e, portanto, seu tempo de duração será certamente não superior a 1 microsegundo, pode mos estimar que o acelerador completará esta tarefa de roteamento em cerca de 200 segundos, ou seja, em menos de 4 minutos. Tipicamente, a solução deste problema de roteamento consome cerca de 3 horas em máquinas do tipo VAX.

O acelerador funciona integrado a um sistema de software AUDE88 que executa as seguintes tarefas: alocação dos componentes a serem terconectados, geração automática de uma crição adequada da superfície a ser utilizada para roteamento a partir de uma descrição dada na forma de texto, ordenação dos sinais a se rem roteados segundo critério de escolha usuário e interface gráfica para visualização dos resultados produzidos pelo roteador hardware. A exceção do alocador, todos os tros programas ja se encontram com seus proto tipos iniciais funcionando. O desenvolvimento de software foi todo feito em microcomputado res nacionais de 16 bits e a linguagem emprega da foi Pascal.

Estima-se que até o final de 1988 o sistema de roteamento completo estará funcionando em mi crocomputadores nacionais de 16 bits. Em 1989 pretende-se iniciar o desenvolvimento de cir cuitos integrados dedicados para implementação dos processadores do acelerador. Com isso, es pera-se que o acelerador apresente um ganho ainda maior em velocidade e, obviamente, pos sua uma implementação em hardware mais compacta.

# REFERÊNCIAS

- [AUDE88] "Sistema de Geração Automática de Lay out com Acelerador de Roteamento", Aude, J. S., Paiva, E.B.M.O., Aude, E.P.L., Lopes, E.P., Martins, M.F., Pinto, S.B., Trabalho a ser publicado nos anais do VIII Congresso da SBC, 1988;

- [BLAN 81] "A Parallel Bit Map Processor Architecture for DA Algorithm", Blank, T., Stefik, M., VanCleemput, W., Proceedings of the 18th Design Automation Conference, Junho, 1981, pp. 837-845;

- [BREU 81] "A Hardware Router", Breuer, M.A., Shamsa, K., Journal of Digital Systems, Vol. 4, no. 4, 1981, pp. 393-408;

- [IOSU 86] "A Class of Array Architectures for Hardware Grid Routers", Iosupovici, A., IEEE

- Transactions on Computer-Aided Design, Vol. CAD-5, No. 2, Abril, 1986, pp. 245-255;

- [LEE 61] "An Algorithm for Path Connections

and its Applications", Lee,C.Y., IRE Trans

actions on Electronic Computers, Vol. EC10, Setembro, 1961, pp. 346-365;

- [RUTE84] "A Class of Cellular Architectures to Support Physical Design Automation", Rutenbar, R.A., Mudge, T.N., Atkins, D.E., IEEE Transactions on Compuer-Aided Design, Vol. CAD-3, No. 4, Outubro, 1984, pp. 264-278;

- [KRAV86] "Multiprocessor Based Placement by

Simulated Annealing", Kravitz,S.A., Ruten

bar,R.A., Proceedings of the 23rd Design

Automation Conference, Junho, 1986, pp.

567-573;

- [PFIS86]"The IBM Yorktown Simulation Engine", Pfister, G.F., Proceedings IEEE, Junho, 1986, pp. 850-860;

- [RYAN87] "An ISMA Lee Router Accelerator, Ryan,T., Rogers,E., IEEE Design and Test of Computers, Outubro, 1987, pp. 38-45;

- [SEIL82] "A Hardware Assisted Design Rule Check Architecture", Seiler, L., Proceedings of the 19th Design Automation Conference, Junho, 1982, pp. 232-238;

- [WON 87] "A Hardware Accelerator for Maze Routing", Won,Y., Sahni,S., E1-Ziq,Y., Proceedings of the 24th Design Automation Conference, Junho, 1987, pp. 800-806.