# TEDA-Multi em FPGA para Processamento Paralelo de Sinais Biomédicos Multissensores

Lucileide M. D. da Silva<sup>\*†</sup>, Sérgio N. Silva<sup>\*‡</sup> e Marcelo A. C. Fernandes<sup>\*§</sup>

<sup>\*</sup>InovaAi Lab, nPITI/IMD, Universidade Federal do Rio Grande do Norte (UFRN), Natal, RN, Brasil

<sup>†</sup>Instituto Federal de Educação, Ciência e Tecnologia do Rio Grande do Norte, Santa Cruz, RN, Brasil

<sup>‡</sup> Unidade Acadêmica de Engenharia Elétrica, UFCG, Campina Grande, PB, Brasil

<sup>§</sup>Departamento de Engenharia da Computação e Automação, UFRN, Natal, RN, Brasil

lucileide.dantas@ifrn.edu.br, sergionatan@dee.ufcg.edu.br e mfernandes@dca.ufrn.br

**Resumo**—Este artigo propõe a arquitetura TEDA-Multi, uma implementação em FPGA do algoritmo TEDA (Typicality and Eccentricity Data Analytics), adaptada para aplicações multissensores na Internet das Coisas Médicas (IoMT). A arquitetura explora a modularidade com múltiplos núcleos paralelos. Experimentos analisaram a potência dinâmica, ocupação de hardware e throughput em diferentes configurações (sensores, frequência, paralelismo). Os resultados demonstram que o TEDA-Multi é escalável, mantém baixo consumo de potência dinâmica em alta densidade de sensores e um bom desempenho em aplicações reais da IoMT com até 80 sensores, sendo compatível com requisitos de sistemas embarcados.

**Index Terms**—TEDA, FPGA, IoMT, Processamento em Tempo Real, Paralelismo, Multissensores

## I. INTRODUÇÃO

A IoMT tem transformado o cenário da saúde, conectando sensores e dispositivos para o monitoramento contínuo de pacientes, especialmente em ambientes críticos como Unidades de Terapia Intensiva (UTIs). A análise eficiente desses fluxos de dados em larga escala apresenta desafios significativos, relacionados à latência, ao consumo energético e à heterogeneidade dos dispositivos. Há uma demanda crítica por arquiteturas otimizadas para dispositivos de borda na IoMT, que combinem baixo consumo energético e alta capacidade de processamento para análise de sinais biomédicos em tempo real [1], [2].

Nesse contexto, dispositivos baseados em Field-Programmable Gate Arrays (FPGAs) mostram-se promissores por oferecerem paralelismo massivo, baixa latência e alta eficiência energética para aplicações em tempo real na área da saúde.

O algoritmo TEDA é uma técnica incremental de baixo custo computacional, originalmente proposta para a detecção de outliers em fluxos de dados [3], [4]. Trabalhos anteriores demonstraram a viabilidade de sua implementação em hardware reconfigurável [5]. Contudo, tais estudos focaram nos aspectos arquiteturais, sem abordar a escalabilidade e o desempenho do algoritmo em cenários com múltiplos sensores, típicos de aplicações da IoMT.

Neste artigo, propõe-se a arquitetura TEDA-Multi, uma implementação do TEDA em FPGA adaptada para análise de dados multissensores na IoMT. O objetivo é investigar a aplicação do TEDA em FPGA, avaliando a escalabilidade do sistema em termos de ocupação de hardware, tempo de

processamento, taxa de transferência (throughput) e consumo, considerando diferentes configurações de sensores e núcleos TEDA paralelos.

## II. DESCRIÇÃO DA PROPOSTA

Este trabalho propõe a arquitetura TEDA-Multi, que é uma extensão da arquitetura apresentada em [5], baseada em uma implementação RTL do algoritmo TEDA em FPGA com suporte a entrada paralela de  $S_n$  sensores por núcleo e pipeline de três estágios para otimizar a taxa de transferência. A TEDA-Multi adapta essa arquitetura para aplicações multissensores na IoMT por meio da replicação de múltiplos núcleos TEDA independentes, permitindo o processamento simultâneo de dados de diversos sensores fisiológicos. Essa abordagem atende aos requisitos de sistemas médicos embarcados, como baixo consumo, alta amostragem e operação em tempo real.

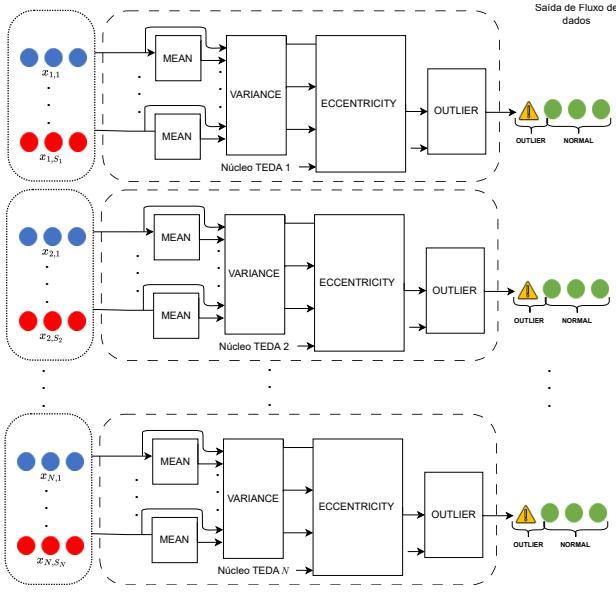

A Figura 1 detalha a arquitetura do TEDA-Multi no qual  $N$  núcleos do TEDA em FPGA são distribuídos de forma paralela. Cada  $n$ -ésimo núcleo mantém os módulos funcionais da versão apresentada em [5], MEAN, VARIANCE, ECCENTRICITY e OUTLIER, organizados em múltiplas instâncias completas e independentes. Cada  $n$ -ésimo núcleo TEDA recebe seu próprio vetor de entrada,  $\mathbf{x}_n$ , composto por  $S$  sinais provenientes de sensores fisiológicos distintos, expresso como

$$\mathbf{x}_n = [x_{n,1}, \dots, x_{n,S_n}] \quad (1)$$

onde  $S_n$  é o número de sensores do  $n$ -ésimo núcleo TEDA. Os dados dos sensores são distribuídos entre os núcleos TEDA, que processam os sinais de forma independente e geram decisões locais sobre cada amostra, classificando-a como normal ou outlier.

## III. METODOLOGIA

A avaliação experimental da proposta teve como objetivo verificar a escalabilidade, o desempenho em tempo real e a eficiência energética da arquitetura TEDA-Multi implementada em FPGA. Sínteses e simulações foram realizadas utilizando o dispositivo Xilinx Virtex-6 (modelo xc6vlx240t-1ff1156), com suporte a ponto flutuante de 32 bits. As etapas de síntese, estimativa de consumo e análise de temporização foram conduzidas com o Xilinx ISE Design Suite.

Figura 1. Visão geral da arquitetura paralela multi-core TEDA proposta.

### A. Configurações Avaliadas

Duas dimensões principais de paralelismo foram exploradas neste trabalho. A primeira refere-se ao número de sensores por núcleo ( $S_n$ ), com avaliações realizadas para configurações contendo 2, 4, 8, 16 e 32 sensores por núcleo. A segunda dimensão diz respeito ao número de núcleos TEDA operando ( $n_{TEDA}$ ) em paralelo, tendo sido implementadas versões com 2, 3, 4, 6 e 8 núcleos independentes.

### B. Métricas de Avaliação

As métricas utilizadas para caracterizar o desempenho e a eficiência da arquitetura foram ocupação de hardware (uso relativo de LUTs, registradores e blocos de multiplicação), latência,  $d$ , tempo de processamento por amostra,  $t_{TEDA}$ , throughput,  $r_{TEDA}$  e potência dinâmica consumida,  $P_{dyn}$ .

A latência,  $d$ , é calculada como  $d = n_p \cdot t_{clk}$ , onde  $n_p$  é o número de estágios do pipeline e  $t_{clk}$  representa o período de clock. O tempo de processamento por amostra,  $t_{TEDA}$ , pode ser expresso como  $t_{TEDA} = 1/f_{clk}$ . O throughput,  $r_{TEDA}$ , é caracterizado como  $r_{TEDA} = f_{clk} \cdot N$ , onde  $N$  corresponde ao número de núcleos TEDA operando em paralelo.

### C. Avaliação Energética

Para estimar o impacto da frequência sobre a eficiência energética da arquitetura, foram conduzidas sínteses adicionais variando a frequência de operação entre 100 kHz e 10 MHz. O consumo de potência dinâmica foi analisado para diferentes quantidades de sensores e núcleos.

## IV. RESULTADOS

A arquitetura paralela TEDA-Multi foi analisada variando o número de sensores por núcleo e a quantidade de núcleos TEDA em paralelo.

### A. Ocupação de Hardware

A Tabela I mostra a ocupação de hardware para múltiplos núcleos TEDA em paralelo, com síntese de configurações de até 8 núcleos contendo 4 sensores cada, respeitando os limites do dispositivo-alvo. Observou-se crescimento linear no uso de LUTs e multiplicadores à medida que o número de entradas aumenta. A baixa ocupação de registradores indica bom potencial para replicação de núcleos TEDA em paralelo. Modelos de regressão linear foram ajustados para estimar o número de multiplicadores ( $n_{MULT}$ ), registradores ( $n_{REG}$ ) e LUTs ( $n_{LUT}$ ) em função da quantidade de sensores por núcleo ( $S_n$ ) e do número de núcleos ( $n_{TEDA}$ ), permitindo prever a ocupação de hardware em configurações não testadas experimentalmente. As Equações 2, 3, e 4 apresentam, as equações de regressão para múltiplos núcleos em paralelo.

$$n_{MULT} = n_{TEDA} \cdot (9 \cdot S_n + 9), \quad (2)$$

$$n_{REG} = n_{TEDA} \cdot (64 \cdot S_n + 693) + 14 \cdot n_{TEDA}^2 + 86, \quad (3)$$

$$n_{LUT} = n_{TEDA} \cdot (3042 \cdot S_n + 5318) + 149. \quad (4)$$

Tabela I

OCUPAÇÃO DE HARDWARE PARA MÚLTIPLOS NÚCLEOS TEDA.

| $n_{TEDA}$ | $S_n$ | $n_{MULT}$ | $n_{REG}$  | $n_{LUT}$    |

|------------|-------|------------|------------|--------------|

| 2          | 2     | 54 (7%)    | 1723 (<1%) | 23006 (15%)  |

| 2          | 4     | 90 (12%)   | 1949 (<1%) | 35441 (23%)  |

| 2          | 8     | 162 (21%)  | 2356 (<1%) | 59966 (39%)  |

| 2          | 16    | 306 (39%)  | 3483 (1%)  | 108632 (72%) |

| 3          | 2     | 81 (10%)   | 2585 (<1%) | 34493 (22%)  |

| 3          | 4     | 135 (17%)  | 2847 (<1%) | 52858 (35%)  |

| 3          | 8     | 243 (31%)  | 3601 (1%)  | 89934 (59%)  |

| 4          | 2     | 108 (14%)  | 3337 (1%)  | 46185 (30%)  |

| 4          | 4     | 180 (23%)  | 3707 (1%)  | 70363 (46%)  |

| 4          | 8     | 324 (42%)  | 4834 (1%)  | 119850 (79%) |

| 6          | 2     | 162 (21%)  | 4863 (1%)  | 68745 (45%)  |

| 6          | 4     | 270 (35%)  | 5719 (1%)  | 105373 (69%) |

| 8          | 2     | 216 (28%)  | 6711 (2%)  | 92133 (61%)  |

| 8          | 4     | 360 (46%)  | 7894 (2%)  | 140275 (93%) |

### B. Tempo de Processamento e Throughput

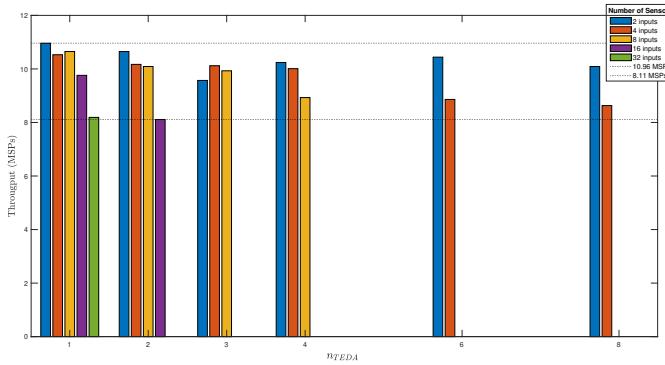

A Tabela II apresenta o tempo de processamento e throughput para múltiplos núcleos TEDA. O tempo crítico ( $T_{clk}$ ) permaneceu na faixa entre 93,9 ns e 122,2 ns, mesmo com o aumento no número de sensores e núcleos, o que é atribuído à simplicidade computacional do TEDA e à eficiência do pipeline em três estágios. O throughput manteve-se elevado (entre 8,11 e 10,65 MSPs), reforçando a eficiência em cenários multissensores em tempo real.

A Figura 2 ilustra a variação do throughput. Observa-se uma leve degradação do desempenho em configurações com maior utilização do FPGA (superior a 80%) devido a limitações no roteamento, mas os resultados permanecem dentro da faixa aceitável para aplicações em tempo real.

### C. Consumo de Potência Dinâmica

A análise da potência dinâmica buscou avaliar a adequação da arquitetura a sistemas embarcados com restrições energéticas típicas da IoMT. A potência dinâmica consumida depende

Tabela II

PROCESSAMENTO E THROUGHPUT PARA MÚLTIPLOS NÚCLEOS TEDA.

| $n_{TEDA}$ | $S_n$ | $t_{clk}$ (ns) | $d$ (ns) | $t_{TEDA}$ (ns) | $r_{TEDA}$ (MSPs) |

|------------|-------|----------------|----------|-----------------|-------------------|

| 2          | 2     | 93,9           | 281,8    | 93,9            | 10,65             |

| 2          | 4     | 98,3           | 294,9    | 98,3            | 10,17             |

| 2          | 8     | 99,1           | 297,3    | 99,1            | 10,09             |

| 2          | 16    | 122,2          | 366,7    | 122,2           | 8,11              |

| 3          | 2     | 104,6          | 313,7    | 104,6           | 9,57              |

| 3          | 4     | 98,8           | 296,4    | 98,8            | 10,12             |

| 3          | 8     | 100,7          | 302,1    | 100,7           | 9,93              |

| 4          | 2     | 97,7           | 293,1    | 97,7            | 10,24             |

| 4          | 4     | 99,9           | 299,6    | 99,9            | 10,01             |

| 4          | 8     | 112,0          | 336,1    | 112,0           | 8,93              |

| 6          | 2     | 95,8           | 287,5    | 95,8            | 10,44             |

| 6          | 4     | 112,8          | 338,5    | 112,8           | 8,86              |

| 8          | 2     | 99,1           | 297,4    | 99,1            | 10,09             |

| 8          | 4     | 115,9          | 347,6    | 115,9           | 8,63              |

Figura 2. Throughput em função do número de sensores e de núcleos TEDA.

fortemente da frequência de operação, sendo sua redução vantajosa para aplicações com baixo consumo e sem restrição de velocidade de processamento.

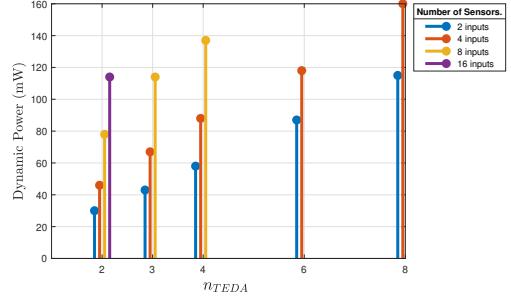

A Tabela III presenta a potência dinâmica operando no maior throughput possível em cada configuração. Devido ao paralelismo estrutural, o throughput permanece similar, mas a potência dinâmica cresce significativamente com a ocupação de recursos do FPGA e da replicação de núcleos, indicando maior custo energético. A Figura 3 ilustra essa variação.

Tabela III

CONSUMO DINÂMICO ( $P_{dyn}$ ) E THROUGHPUT ( $r_{TEDA}$ ) EM FUNÇÃO DE NÚCLEOS TEDA ( $n_{TEDA}$ ) E SENsoRES ( $S_n$ ).

| $n_{TEDA}$ | $S_n$ | $P_{dyn}$ (mW) | $r_{TEDA}$ (MSPs) |

|------------|-------|----------------|-------------------|

| 2          | 2     | 30             | 10,65             |

| 2          | 4     | 46             | 10,17             |

| 2          | 8     | 78             | 10,09             |

| 2          | 16    | 114            | 8,11              |

| 3          | 2     | 43             | 9,57              |

| 3          | 4     | 67             | 10,12             |

| 3          | 8     | 114            | 9,93              |

| 4          | 2     | 58             | 10,24             |

| 4          | 4     | 88             | 10,01             |

| 4          | 8     | 137            | 8,93              |

| 6          | 2     | 87             | 10,44             |

| 6          | 4     | 118            | 8,86              |

| 8          | 2     | 115            | 10,09             |

| 8          | 4     | 160            | 8,63              |

Figura 3. Potência dinâmica em função de sensores e de núcleos TEDA.

Tabela IV

POTÊNCIA DINÂMICA (EM MW) PARA MÚLTIPLOS NÚCLEOS TEDA ( $n_{TEDA}$ ), EM FUNÇÃO DAS FREQUÊNCIAS ( $f$ ) E SENsoRES ( $S_n$ ).

| $n_{TEDA}$ | $f$ (MHz) | Número de sensores de entrada, $S_n$ |     |     |     |

|------------|-----------|--------------------------------------|-----|-----|-----|

|            |           | 2                                    | 4   | 8   | 16  |

| 2          | 1,0       | 3                                    | 5   | 8   | 14  |

|            | 2,0       | 6                                    | 9   | 16  | 29  |

|            | 3,0       | 9                                    | 14  | 23  | 43  |

|            | 5,0       | 14                                   | 23  | 39  | 72  |

|            | 8,0       | 23                                   | 37  | 62  | 114 |

|            | 10,0      | 28                                   | 46  | 78  | —   |

| 3          | 1,0       | 5                                    | 7   | 12  | —   |

|            | 2,0       | 9                                    | 13  | 23  | —   |

|            | 3,0       | 14                                   | 20  | 35  | —   |

|            | 5,0       | 23                                   | 34  | 58  | —   |

|            | 8,0       | 36                                   | 54  | 93  | —   |

|            | 10,0      | —                                    | 67  | —   | —   |

| 4          | 1,0       | 6                                    | 9   | 16  | —   |

|            | 2,0       | 11                                   | 18  | 31  | —   |

|            | 3,0       | 17                                   | 27  | 47  | —   |

|            | 5,0       | 28                                   | 45  | 78  | —   |

|            | 8,0       | 46                                   | 72  | 125 | —   |

|            | 10,0      | 57                                   | 88  | —   | —   |

| 6          | 1,0       | 8                                    | 13  | —   | —   |

|            | 2,0       | 17                                   | 27  | —   | —   |

|            | 3,0       | 25                                   | 40  | —   | —   |

|            | 5,0       | 42                                   | 67  | —   | —   |

|            | 8,0       | 67                                   | 108 | —   | —   |

|            | 10,0      | 84                                   | —   | —   | —   |

| 8          | 1,0       | 11                                   | 19  | —   | —   |

|            | 2,0       | 23                                   | 38  | —   | —   |

|            | 3,0       | 34                                   | 57  | —   | —   |

|            | 5,0       | 57                                   | 94  | —   | —   |

|            | 8,0       | 91                                   | 151 | —   | —   |

|            | 10,0      | 113                                  | —   | —   | —   |

A Tabela IV apresenta a potência dinâmica para implementações multicore em diferentes frequências. Observa-se que o consumo de energia aumenta com a frequência de operação, com o número de sensores por núcleo e com a quantidade de núcleos. A ausência de resultados em algumas configurações indica (i) a configuração excede os recursos disponíveis do FPGA-alvo, inviabilizando sua implementação; ou (ii) a arquitetura não foi capaz de atingir a frequência especificada devido à complexidade da implementação.

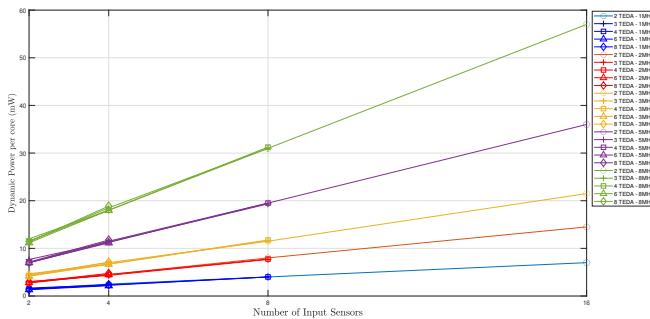

A quantidade de núcleos e sensores de entrada e a frequência de operação impactam o consumo de potência e a ocupação de recursos no FPGA. A Tabela IV sugere que, em uma mesma frequência, a potência dinâmica cresce linearmente com o número de núcleos. A Figura 4 reforça essa ideia, mostrando

que o consumo dinâmico por núcleo é praticamente constante, independentemente da quantidade total de núcleos ativos, pois as curvas associadas a uma mesma frequência se sobrepõem, o que evidencia que o consumo por núcleo permanece praticamente constante, independentemente da quantidade total de núcleos ativos.

Assim, o consumo total de potência dinâmica em arquiteturas multicore pode ser estimado por

$$P_{dyn}(n_{TEDA}) = n_{TEDA} \cdot f \cdot (0,667 + 0,4167 \cdot S_n). \quad (5)$$

Figura 4. Potência dinâmica por núcleo em função do número de sensores de entrada para diferentes frequências de operação em implementações multicore.

As Figuras 3 e 4 complementam a análise energética da proposta multicore, demonstrando que o consumo total aumenta linearmente com sensores e núcleos. Mas que é mais fortemente influenciada pela frequência de operação, destacando a importância da limitação de clock para baixo consumo. Para sinais fisiológicos lentos, a subamostragem e a multiplexação temporal (reuso sequencial de núcleos TEDA para diferentes canais) são estratégias de escalabilidade viáveis e energeticamente eficientes.

#### *D. Aplicações Multissensores*

Em ambientes de IoMT (múltiplos sensores em tempo real) como por exemplo, sistemas hospitalares, a arquitetura TEDA-multi se mostra promissora, especialmente por seu desempenho e baixo consumo. Com  $t_{clk} = 125$  ns e 32 entradas paralelas, estima-se o processamento de 5.120.000 sensores por segundo (com taxa de 50 amostras/s) via replicação e multiplexação, evidenciando a escalabilidade da solução.

Foram exploradas aplicações médicas com diferentes níveis de complexidade sensorial, incluindo ECG tradicional com 12 derivações, sistemas vestíveis com 8 canais [6] e sistemas de alta densidade com 80 derivações [7]. As Tabelas V e VI apresentam as estimativas de ocupação e consumo dinâmico para esses cenários.

Tabela V

| Referência  | $S_n$ | $n_{MULT}$ | $n_{REG}$  | $n_{LUT}$      |

|-------------|-------|------------|------------|----------------|

| ECG         | 12    | 117 (15%)  | 1450 (<1%) | 42,187 (28%)   |

| Tradicional | 8     | 81 (11%)   | 1189 (<1%) | 29,963 (19%)   |

| [6]         | 80    | 729 (95%)  | 6006 (2%)  | 250,131 (165%) |

| [7]         |       |            |            |                |

**Tabela VI**

**POTÊNCIA DINÂMICA EM APLICAÇÕES MULTISSENSORES.**

| Referência  | $S_n$ | Amostragem (Hz) | $P_{dyn}$ ( $\mu\text{W}$ ) |

|-------------|-------|-----------------|-----------------------------|

| ECG         | 12    | 1000            | 5,67                        |

| Tradicional |       | 250             | 1,41                        |

| [6]         | 8     | 200             | 0,8                         |

| [7]         | 80    | 1000            | 34                          |

|             |       | 250             | 8,5                         |

Sistemas com 80 canais excederam os recursos da FPGA utilizada. A solução proposta foi a divisão do sistema em dois FPGAs, cada um configurado com dois núcleos TEDA cada (entradas de 29/12 e 29/10 sensores). Além disso, a multiplexação temporal é viável para sinais de baixa amostragem (ex.: ECG 500 Hz), permitindo que o mesmo núcleo atenda múltiplos pacientes ou regiões sensoriais com custo computacional reduzido. Esses resultados evidenciam a viabilidade da arquitetura TEDA em sistemas vestíveis, dispositivos portáteis e ambientes hospitalares intensivos, onde confiabilidade, baixa latência e baixo consumo energético são críticos.

## V. CONCLUSÕES

Os resultados comprovam a viabilidade da arquitetura TEDA multicore em FPGA para aplicações multissensores na IoMT. A principal contribuição é um sistema escalável, com suporte à replicação paralela e baixo consumo de potência. A escalabilidade é evidenciada pelo consumo de potência por núcleo que se mantém constante em diferentes configurações, permitindo a expansão para mais sensores sem perda de desempenho individual. O baixo consumo dinâmico e a possibilidade de otimizações (subamostragem/multiplexação) reforçam sua adequação para sistemas embarcados de tempo real na IoMT, oferecendo uma solução eficiente, escalável e energeticamente viável para processamento paralelo de sinais biomédicos.

## REFERÊNCIAS

- [1] Z. Mao, C. Liu, Q. Li, Y. Cui, and F. Zhou, "Intelligent intensive care unit: Current and future trends," *Intensive Care Research*, vol. 3, no. 2, pp. 182–188, 2023.

- [2] I. Ben Dhaou, M. Ebrahimi, M. Ben Ammar, G. Bouattour, and O. Kounou, "Edge devices for internet of medical things: Technologies, techniques, and implementation," *Electronics*, vol. 10, no. 17, 2021.

- [3] B. S. J. Costa, C. G. Bezerra, L. A. Guedes, and P. P. Angelov, "Online fault detection based on typicality and eccentricity data analytics," in *2015 International Joint Conference on Neural Networks (IJCNN)*, July 2015, pp. 1–6.

- [4] P. Angelov, "Anomaly detection based on eccentricity analysis," in *2014 IEEE Symposium on Evolving and Autonomous Learning Systems (EALS)*, Dec 2014, pp. 1–8.

- [5] L. M. D. Da Silva, M. G. F. Coutinho, C. E. B. Santos, M. R. Santos, M. D. Ruiz, L. A. Guedes, and M. A. C. Fernandes, "Hardware architecture proposal for teda algorithm to data streaming anomaly detection," *IEEE Access*, vol. 9, pp. 103 141–103 152, 2021.

- [6] M. A. Meghravi, Y. Tian, A. Mahnam, P. Bhattachan, L. Eskandarian, S. T. Kakhki, M. R. Popovic, and M. Lankarany, "Multichannel ecg recording from waist using textile sensors," *BioMedical Engineering OnLine*, vol. 19, p. 48, 2020.

- [7] R. Marcinkevics, J. O'Neill, H. Law, E. Pervolaraki, A. Hogarth, C. Russell, B. Stegemann, A. V. Holden, and M. H. Tayebjee, "Multichannel electrocardiogram diagnostics for the diagnosis of arrhythmogenic right ventricular dysplasia," *EP Europace*, vol. 20, no. FI1, pp. f13–f19, 08 2017.