# Estudo de Transistores pMOS/nMOS SOI MuGFETs Baseado em Simulações Numéricas 2D e Caracterização Elétrica

Abstract. The focus of this paper is to present an analysis among double gate transistors for different channel lengths comparing the performance of pMOS and nMOS transistors. The main electrical parameters such as threshold voltage, subthreshold slope, transconductance and DIBL are presented. The results have been obtained to compare the efficiency and the behavior of these different transistors using 2D numerical simulations and electrical characterization. The results show that nMOS transistor with thin silicon film thickness have better performance and reduced short channel effects compared to the pMOS devices.

**Resumo.** O foco deste artigo é apresentar uma análise entre transistores de porta dupla para diferentes comprimentos de canal comparando o desempenho de dispositivos pMOS e nMOS. Os principais parâmetros elétricos tais como tensão de limiar, inclinação de sublimiar, transcondutância e DIBL são apresentados. Os resultados foram obtidos comparando a eficiência e o comportamento de tais transistores através de simulações numéricas 2D e caracterização elétrica. Os resultados mostraram que os transistores nMOS com fina espessura do filme de silício apresentam, em relação aos dispositivos pMOS, melhor performance e reduzidos efeitos de canal curto.

# 1. Introdução

Historicamente, observa-se na evolução da microeletrônica, a coerência dos fatos em relação à Lei de Moore, gerando como resultado circuitos integrados cada vez menores, porém com uma maior quantidade de transistores e melhor desempenho. A busca atualmente é o aperfeiçoamento do dispositivo principalmente quanto a desempenho e velocidade e para isso, tem-se alterado fortemente sua geometria [Colinge 2004]. No entanto, o que vem sendo observado ao longo dos anos, é que dispositivos menores são mais difíceis de serem fabricados, além de apresentarem efeitos parasitários conhecidos como efeitos de canal curto (*short channel effects* – SCE).

Dentre os efeitos de canal curto pode-se citar o DIBL (*Drain Induced Barrier Lowering* – efeito de abaixamento de barreira induzido pelo dreno), responsável pela queda na tensão de limiar decorrente do aumento no potencial de dreno. A inclinação de sublimiar é degradada e a tensão de limiar diminui para pequenos comprimentos de canal. A fim de evitar tais efeitos indesejáveis, novas tecnologias são desenvolvidas, como é o caso dos dispositivos que utilizam Silício sobre Isolante (SOI MOSFET). Os SOI MOSFETs substituem as lâminas (*wafer*) de silício convencionais por lâminas do tipo SOI aumentando o controle das cargas na região do canal [Colinge 2004].

Em segunda instância, a evolução dos dispositivos de porta múltipla descreve a influência da tensão de porta no controle do canal e, portanto, na performance do dispositivo. Efeitos de canal curto são reduzidos quando mais de uma porta é construída entorno do canal [Colinge 2008].

Dando continuidade a teoria do controle do canal pela porta, a tecnologia UTB (*Ultra-thin Body*) tem ganhado força e apresentado resultados vantajosos. Tais dispositivos mostram-se eficazes em evitar efeitos de canal curto e em melhorar o nível de corrente através de uma espessura de filme de silício muito fina, aumentando o desempenho no controle de cargas [Colinge 2004].

Utilizando simulações numéricas bidimensionais, o objetivo deste artigo é obter um estudo comparativo entre os principais parâmetros elétricos dos transistores MuGFETs pMOS e nMOS. Os resultados foram confrontados com medidas experimentais obtidas em transistores SOI de porta tripla.

## 2. Simulações Numéricas

O simulador numérico usado neste trabalho foi o ATLAS da Silvaco [ATLAS 2010]. Este simulador usa modelos matemáticos baseados nas equações físicas, permitindo a extração de diferentes parâmetros e condições de polarização. Foram considerados modelos de mobilidade, dependência do campo elétrico paralelo, estreitamento no bandgap (banda proibida) e de recombinação levando em conta o tempo de vida dos portadores (teoria Shockley-Read-Hall).

As condições dos dispositivos utilizadas nas simulações são apresentadas na tabela 1 e são baseadas em [Collaert 2007]. Porém, as simulações consideram uma estrutura bidimensional, negligenciando os efeitos de variação na largura de canal. Os impactos de diferentes comprimentos de canal e espessuras do filme de silício são analisados em ambos os tipos de transistores: nMOS e pMOS.

Tabela 1. Condições dos parâmetros simulados

| Parâmetros                                                             | Valores                             |

|------------------------------------------------------------------------|-------------------------------------|

| Comprimento de Canal (L)                                               | 30 ~ 410 nm                         |

| Espessura do Filme de Silício (t <sub>Si</sub> )                       | 30, 60 nm                           |

| Espessura do Óxido de Porta (t <sub>oxf</sub> )                        | 2 nm                                |

| Espessura do Óxido Enterrado (t <sub>oxb</sub> )                       | 150 nm                              |

| Concentração Região Naturalmente Dopada (Na)                           | 1x10 <sup>15</sup> cm <sup>-3</sup> |

| Concentração Região de Fonte e Dreno (N <sub>d</sub> /N <sub>a</sub> ) | 1x10 <sup>20</sup> cm <sup>-3</sup> |

|                                                                        | 1x10 <sup>19</sup> cm <sup>-3</sup> |

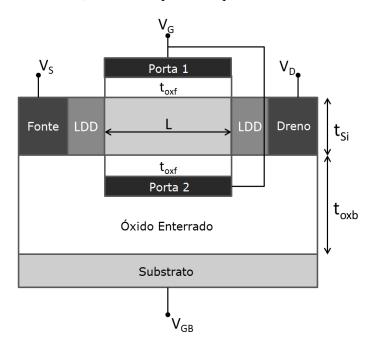

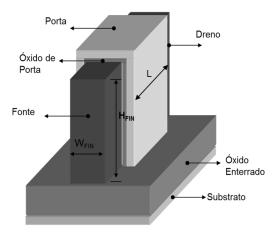

A estrutura do dispositivo utilizado nas simulações é representada no perfil em corte transversal da figura 1. A mesma estrutura foi simulada nos dois tipos de transistores pMOS e nMOS, alterando apenas o tipo de material em cada situação.

Figura 1. Perfil estrutural de um transistor de porta dupla.

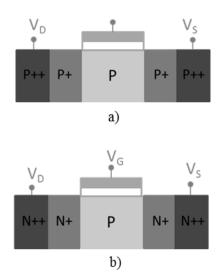

No caso pMOS, a concentração de dopantes de toda a estrutura é formada por material tipo P, já que o canal é naturalmente dopado, de acordo com [Collaert 2007]. Consequentemente os dispositivos pMOS assumem uma configuração P+/P/P+ enquanto que o nMOS apresenta conhecida configuração N+/P/N+, conforme ilustrado na figura 2.

Figura 2. Perfil da configuração de dopagem dos transistores a) pMOS e b)nMOS.

## 3. Resultados das Simulações

Conforme posteriormente dito, o foco deste estudo são as diferenças entre dispositivos pMOS e nMOS em termos de seus parâmetros elétricos específicos. Os resultados obtidos nas simulações são descritos nos itens abaixo.

## 3.1. Tensão de Limiar – V<sub>TH</sub>

Esse parâmetro é um dos mais importantes no estudo do transistor. É a tensão mínima para a qual o dispositivo inicia a condução efetiva de corrente, responsável pela inversão dos portadores na região de canal.

O método utilizado para retirar das simulações o  $V_{TH}$ , foi realizado a partir do traçado do gráfico da segunda derivada de  $I_{DS}$  x  $V_{GS}$ , onde o pico máximo é a tensão desejada.

A função trabalho (*work function*) adotada nas simulações é relacionada ao nitreto de titânio, metal de porta presente no processo em [Collaert 2007]. Em todos os ensaios, o valor de V<sub>TH</sub> se manteve em torno de 0,44V, com oscilação de menos de 10% para variações de comprimento do canal. A espessura do filme de silício contribui com a estabilidade desses valores por causa do melhor controle eletrostático das cargas na região do canal.

## 3.2. Transcondutância – gm

A transcondutância foi obtida a partir da derivada da curva  $I_{DS}$  x  $V_{GS}$ . A curva deste parâmetro nos permite fazer uma análise a respeito do controle da porta sobre as cargas presentes na região do canal.

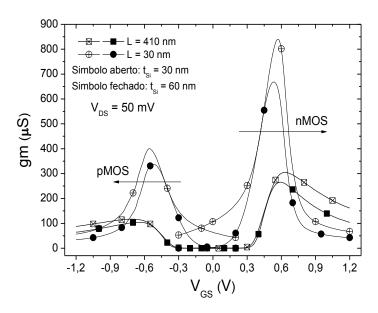

Figura 3. Transcondutância em função da tensão de porta para comprimentos de canal longo e curto e com t<sub>si</sub> de 30 e 60 nm.

Transistores nMOS apresentaram valores mais elevados de gm do que os dispositivos pMOS de geometria análoga, conforme figura 3, o que significa que uma maior mobilidade dos elétrons afeta diretamente o controle das cargas desde que as dimensões sejam as mesmas para ambos os dispositivos.

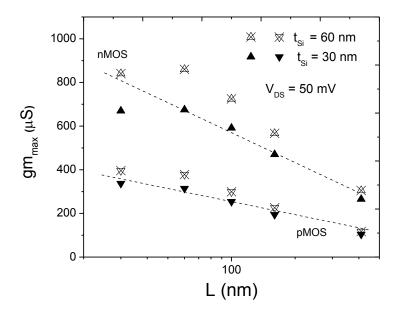

A influência da espessura do filme de silício aumenta o nível de gm devido a uma melhor condução de corrente para menor  $t_{\rm Si}$ . O valor de pico da transcondutância em função do comprimento do canal (figura 4) mostra um acréscimo nos valores para dispositivos menores, conforme o esperado. O ligeiro decréscimo para  $t_{\rm Si}$  de 30 nm no dispositivo nMOS pode ser justificado pela influência de uma resistência parasita em serie que se torna significativa em tal dimensão.

Figure 4. Valor máximo da transcondutância em função do comprimento do canal para t<sub>si</sub> de 30 nm e 60 nm.

## 3.3. Inclinação de Sublimiar – S

A Inclinação de submiliar foi extraída do inverso da derivada da curva de  $I_{DS}$  x  $V_{GS}$  em regime de sublimiar, considerando uma curva logarítmica em um só eixo.

A inclinação de sublimiar é definida como a eficiência do chaveamento do transistor é desejada como um pequeno valor o que implica em transistores mais rápidos. Os valores de S estão apresentados na tabela 2. O acoplamento das portas é responsável pela melhora no comportamento observado quando um filme de silício muito fino é utilizado. A diferença obtida é cerca de cinco vezes menor para espessuras de 30 nm em dispositivos com L grande. Os efeitos de comprimento de canal mostram uma grande influência na inclinação de sublimiar, aumentando seu valor para comprimentos menores. A diferença entre pMOS e nMOS ocorre devido as diferentes mobilidades dos portadores de cada estrutura.

| Tabela 2. Inclinação de Sublimiar para diferentes valores de comprimento de canal e |

|-------------------------------------------------------------------------------------|

| espessura do filme de silício.                                                      |

|          | Inclinação de Sublimiar (mV/dec) |                          |                          |                          |  |

|----------|----------------------------------|--------------------------|--------------------------|--------------------------|--|

| L (nm)   | L (nm) pMOS                      |                          | nMOS                     |                          |  |

| L (IIII) | $t_{Si} = 30 \text{ nm}$         | $t_{Si} = 60 \text{ nm}$ | $t_{Si} = 30 \text{ nm}$ | $t_{Si} = 60 \text{ nm}$ |  |

| 30       | 168                              | 893                      | 161                      | 858                      |  |

| 60       | 75                               | 167                      | 74                       | 158                      |  |

| 100      | 64                               | 86                       | 63                       | 83                       |  |

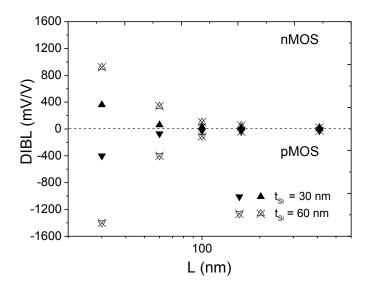

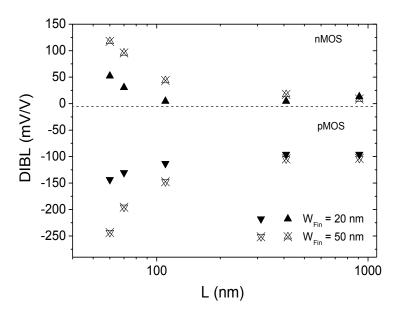

#### 3.4. Drain Induced Barrier Lowering (DIBL).

Este parâmetro descreve a alteração da tensão de limiar quando se aumenta a tensão do dreno. Essa mudança é mais negativamente significativa em dispositivos de canal curto e é calculado pela equação 1 [Santos 2009], considerando duas tensões de dreno diferentes: 50 mV e 1,2 V. Os valores de tensão de limiar foram extraídos através do método de nível de corrente.

$$DIBL(mV/V) = \frac{V_{TH1(VD1)} - V_{TH2(VD2)}}{V_{D2} - V_{D1}}$$

(1)

Pode-se observar na figura 5 que, para grandes valores de comprimento de canal e fina camada de silício, nenhuma variação significativa de  $V_{TH}$  é verificada. Nos canais de comprimento inferior a 70 nm, o efeito de DIBL é altamente pronunciado, no caso para  $t_{Si}=60$  nm onde a penetração das linhas de campo do dreno é maior se comparada a descrita em  $t_{Si}=30$  nm devido ao menor acoplamento das portas, causando uma variação na tensão de limiar.

A comparação entre pMOS e nMOS pode ser analisada através do valor absoluto da variação e considerando o menor comprimento de canal em  $t_{\rm Si}$  =60 nm. Na condição descrita, o dispositivo pMOS apresenta aproximadamente 0,5 V/V de crescimento se comparado ao valor de um dispositivo nMOS. Quando um filme fino de silício é considerado, essa diferença se reduz a 40 mV/V, confirmando uma maior influência do efeito de campo elétrico paralelo na região de canal em filmes de menor espessura de

silício. A porcentagem de variação do DIBL ao longo do canal é 51% para pMOS e 46% para nMOS com 60 nm de  $t_{Si}$ . Os valores são reduzidos para 19% e 17% respectivamente, para os dispositivos de menor espessura do filme de silício.

Figure 5. DIBL em função do comprimento de canal e da espessura do filme de silício.

# 4. Resultados Experimentais

A caracterização elétrica foi feita utilizando do equipamento HP4156C. Os dispositivos foram fabricados no Imec (Interuniversity Microeletronics Center) na Bélgica e são transistores de porta tripla não planares.

Os dispositivos medidos possuem cinco filetes de silício (ou simplesmente *fins*, ou seja,  $N_{\rm fin}=5$ ) e suas principais características são apresentadas na tabela 1, exceto para comprimento de canais variando entre 60 nm e 910 nm. O maior número de *fins* em paralelo permite um aumento do nível de corrente do transistor. Esse fator não foi considerado nas simulações. A largura total ( $W_{\rm eff}$ ) de um transistor não planar é dada por  $2H_{\rm fin}+W_{\rm fin}$ . A figura 6 representa o transistor de porta tripla com suas definições geométricas.

Figure 6. Representação esquemática de um transistor de porta tripla.

Os transistores foram medidos polarizando o dreno com potenciais baixo (50 mV) e alto (1,2 V). A tensão de porta ( $V_{GS}$ ) foi variada de 0 a 1,2 V. No caso de dispositivos de porta tripla, a terceira porta proporciona uma melhora no comportamento do dispositivo e, portanto, não é possível estabelecer uma comparação direta entre as simulações e os dados experimentais. Assim, fica fora do escopo deste artigo comparar os resultados diretamente, dado que para isso seriam necessários ajustes mais elaborados e simulações 3D. Entretanto, as tendências nos resultados podem ser analisadas e comparadas a fim de estimar a confiabilidade das simulações. Neste artigo a espessura do filme silício é equivalente à altura do *fin* ( $H_{fin}$ ) para a condição de 60 nm que é a mesma para todos os dispositivos foram medidos. Contudo é comum associar a largura do fin ( $W_{fin}$ ) ao parâmetro  $t_{Si}$  dado que é a distancia entre as portas [Colinge 2008]. Portanto, a variação na largura do fin apresenta efeito similar ao observado no decréscimo de  $t_{Si}$ . Consequentemente, como se tem duas larguras de *fin* diferentes na escala de transistores medidos é possível confrontar, qualitativamente, os dois resultados, experimental e simulado.

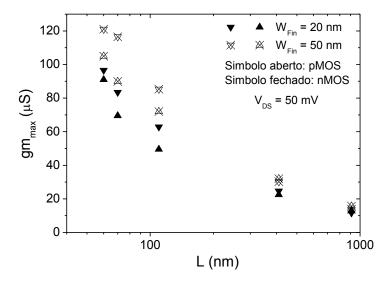

## 4.1 Transcondutância – gm

Na figura 7, a transcondutância máxima não segue a mesma tendência obtida nas simulações numéricas. A explicação pode ser associada ao fato de os dispositivos medidos serem de porta tripla e a mobilidade entre as laterais e o topo do *fin* não serem iguais devido às diferentes orientações cristalográficas. Como resultado, existe uma competição do tipo do material e também uma influência da largura do *fin* que definem o nível de corrente e o comportamento da transcondutância.

Experimentalmente, dispositivos pMOS apresentam maiores valores de gm<sub>max</sub>, considerando as estruturas menores, devido à maior mobilidades das lacunas nas paredes do *fin* que apresenta orientação cristalográfica (110). A mobilidade dos elétrons é melhor na orientação (100) que, neste caso, aparece apenas no topo do *fin*. A diferença entre nMOS e pMOS é em torno de 15% para transistores mais largos e de 7% para os finos.

Figura 7. Máxima transcondutância em função do comprimento de canal.

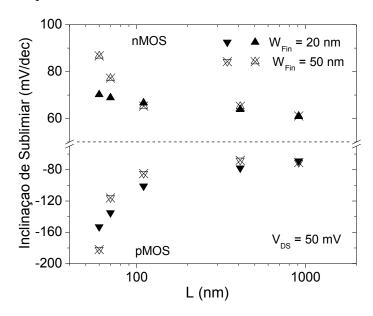

## 4.2 Inclinação de Sublimiar - S

Os valores de inclinação de sublimiar podem ser observados na figura 8 onde a influência das diferentes larguras de *fin* é comparada àsdiferentes espessuras do filme de silício. Filmes mais estreitos melhoram o comportamento do dispositivo devido ao melhor acoplamento eletrostático assim como nos filmes finos. Os valores de inclinação de sublimiar são menores para dispositivos nMOS por causa da diferença de mobilidade dos portadores na comparação com pMOS, considerando um regime exponencial de sublimiar. A diferença vista entre pMOS e nMOS é de valores aproximadamente duas vezes maiores no primeiro caso.

Figura 8. Inclinação de sublimiar em função do comprimento do canal para diferentes larguras de canal.

## 4.3. Drain Induced Barrier Lowering (DIBL)

Os valores de DIBL estão apresentados na figura 9 e seu comportamento é similar ao obtido nas simulações, onde as diferenças nos valores absolutos são relacionadas ao conjunto de abordagens e as propriedades dos dispositivos tridimensionais reais. Diminuindo o comprimento de canal, o DIBL aumenta por causa de uma maior interação do campo elétrico do dreno com as cargas da região do canal. É também observado que a maior variação do DIBL, para transistores de canal curto, ocorre em dispositivos pMOS, principalmente para fina espessura de filme de silício, onde se tem 52% de aumento em relação aos nMOS. Uma razão possível para explicar esse comportamento pode estar relacionada aos diferentes coeficientes de difusão de cada dopante que alteraria o perfil de cargas da região do canal.

Figura 9. DIBL em função do comprimento do canal para diferentes valores de espessura do filme de silício

#### 5. Conclusão

Este artigo analisa os principais parâmetros elétricos, tais como tensão de limiar, transcondutância, inclinação de sublimiar e DIBL. O estudo foi feito baseado na comparação entre dispositivos pMOS e nMOS, variando a espessura do filme de silício em diferentes comprimentos de canal. Observou-se que os transistores do tipo pMOS são mais susceptíveis a efeitos de canal curto, apresentando maiores valores de DIBL e S tanto nas simulações quanto nos resultados experimentais, provavelmente, devido ao diferente perfil de cargas de cada estruturas. Entretanto, a transcondutância máxima dos dispositivos reais mostrou-se melhor (maior) nos transistores pMOS devido à maior mobilidade das lacunas nas paredes do *fin* que não foi considerada nas simulações em 2D.

Dispositivos projetados com fina espessura da camada de silício foram muito mais eficientes em todo o conjunto de parâmetros estudados, melhorando o comportamento do transistor em termos de efeitos do canal curto e nível de corrente devido ao melhor acoplamento eletrostático na região do canal. A mesma tendência foi alcançada quando a largura do *fin* foi variada nas medidas experimentais. Comparando os dados experimentais aos simulados, a mesma tendência foi observada entre eles. As discrepâncias que, inevitavelmente, apareceram derivaram do fato de que os dispositivos reais apresentavam estrutura tridimensional não planar, enquanto as simulações foram baseadas em estruturas bidimensionais que não foram ajustadas para trabalharem como os dispositivos reais. Consequentemente, a diferença da mobilidade dos portadores no topo e nas laterais do *fin* e a influência da largura do *fin* contribuíram para as diferenças obtidas.

# 6. Referências

- Colinge, J. P. (2004), Silicon-On-Insulator Technology. Materials to VLSI, 3<sup>rd</sup> ed, Kluwer, Boston, MA.

- Santos, S. D. et al. (2009), "DIBL Study Using Triple Gate Unstrained and Uniaxial/Biaxial Strained FinFETs", ECS Transactions, Pennington, NJ, 23, pp. 591-596.

- Colinge, J. P. (2008), FinFETs and other Multi-Gate Transistors, *1<sup>st</sup> ed*, Kluwer, Boston, MA.

- ATLAS Device Simulator (2010), User's Manual, 5.14.0, Silvaco International, Santa Clara, CA.

- Collaert, N. et al. (2007), "Stress hybridization for multigate devices fabricated on supercritical strained-SOI (SC-SSOI)", IEEE Electron Device Letters, 28, pp. 646-648, 2007.